# Essentials Of Computer Architecture

Prof. Douglas Comer Computer Science And ECE Purdue University

http://www.cs.purdue.edu/people/comer

Copyright © 2017 by Douglas Comer. All rights reserved

### Module I

#### Course Introduction And Overview

# **The Big Questions**

• Most CS programs require an architecture course, but you might ask:

# **The Big Questions**

• Most CS programs require an architecture course, but you might ask:

# Is knowledge of computer organization and the underlying hardware relevant these days?

Should we take this course seriously?

#### The Answers

- Companies (such as Google, IBM, Microsoft, Apple, Cisco,...) look for knowledge of architecture when hiring (i.e., understanding computer architecture can help you land a job)

- The most successful software engineers understand the underlying hardware (i.e., knowing about architecture can help you earn promotions)

- As a practical matter: knowledge of computer architecture is needed for later courses, such as systems programming, compilers, operating systems, and embedded systems

• Traditional software engineering jobs are saturated

- Traditional software engineering jobs are saturated

- The future lies in embedded systems

- Cell phones

- Video games

- MP3 players

- Set-top boxes

- Smart sensor systems

- Traditional software engineering jobs are saturated

- The future lies in embedded systems

- Cell phones

- Video games

- MP3 players

- Set-top boxes

- Smart sensor systems

- Understanding architecture is key for programming embedded systems

#### **Some Bad News About Architecture**

#### **Some Bad News About Architecture**

- Hardware is ugly

- Lots of low-level details

- Can be counterintuitive

- Hardware is tricky

- Timing is important

- A small addition in functionality can require many pieces of hardware

- The subject is so large that we cannot hope to cover it in one course

- You will need to think in new ways

#### **Some Good News About Architecture**

#### **Some Good News About Architecture**

- You will learn to think in new ways

- It is possible to understand basics without knowing all low-level technical details

- Programmers only need to learn the essentials

- Characteristics of major components

- Role in overall system

- Consequences for software

### **The Four Main Topics**

- Basics of digital hardware

- You will build a few simple circuits

- Processors

- You will program RISC and CISC processors in lab

- Memories

- You will learn about memory organization and caching

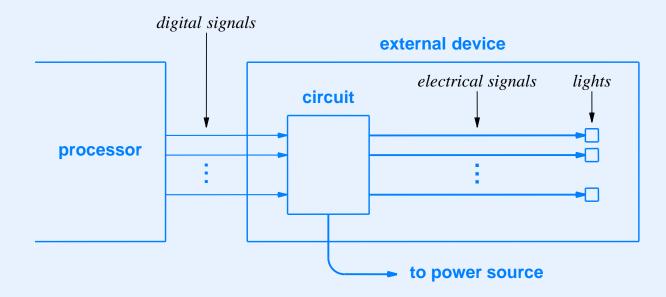

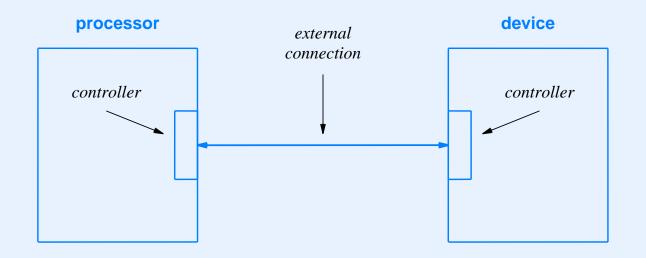

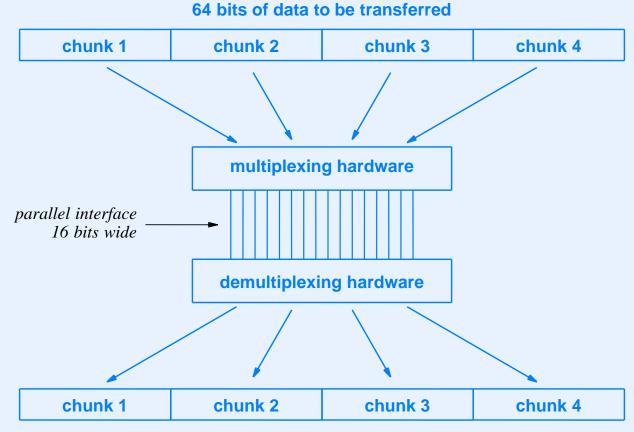

- I/O operates

- You will explore buffering and learn about interrupts

# **Organization Of The Course**

- Basics

- A taste of digital logic

- Data paths and execution

- Data representations

- Processors

- Instruction sets and operands

- Assembly languages and programming

- Memories

- Physical and virtual memories

- Addressing and caching

# Organization Of The Course (continued)

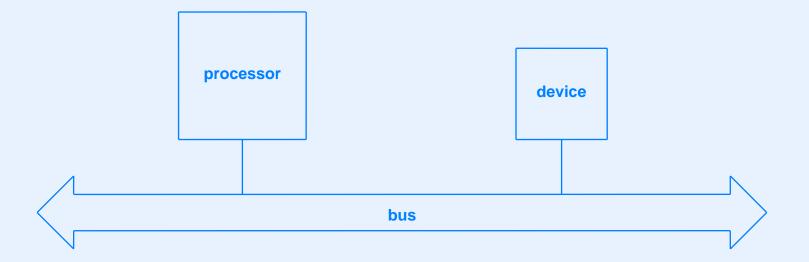

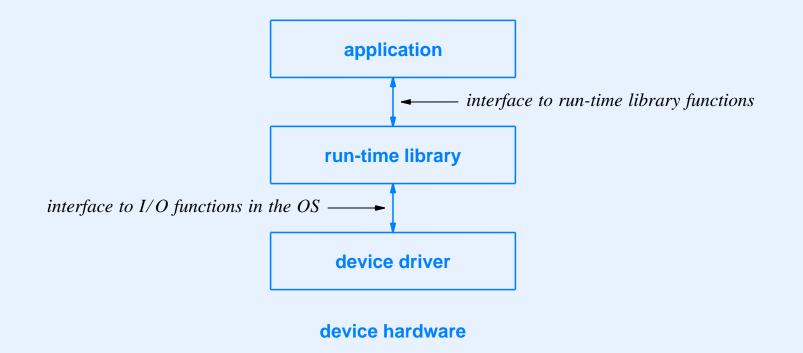

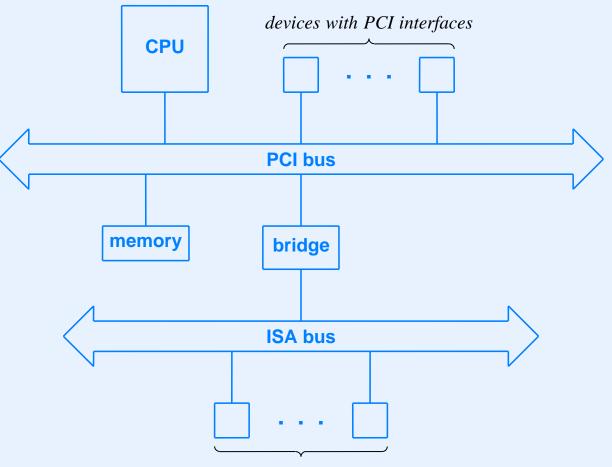

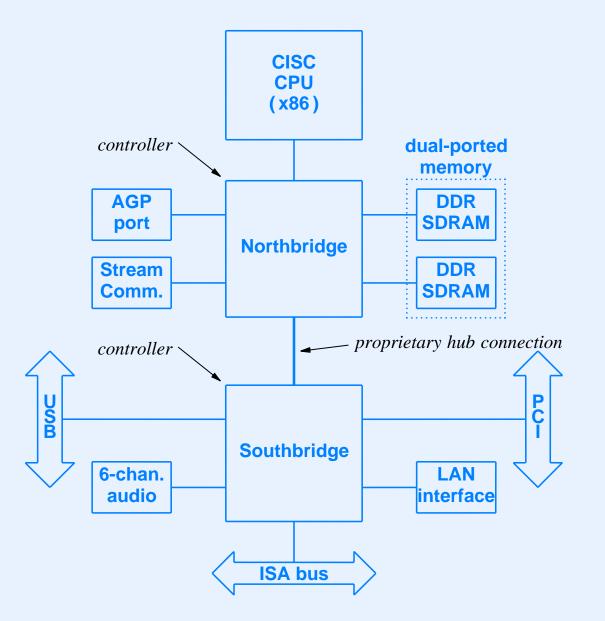

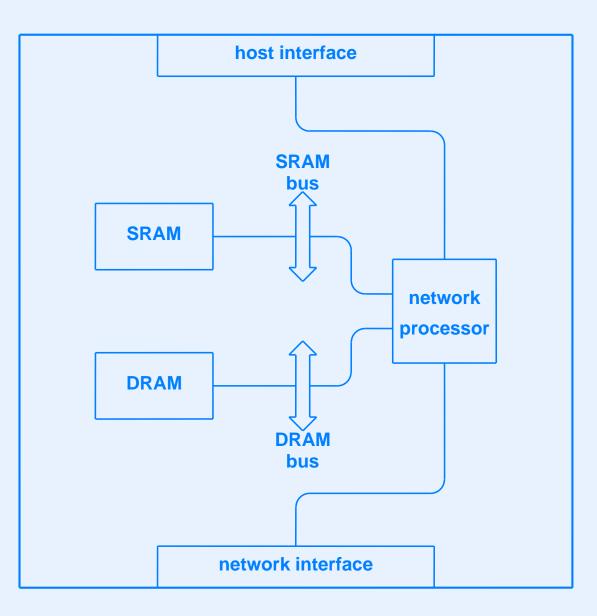

- Input/Output

- Devices and interfaces

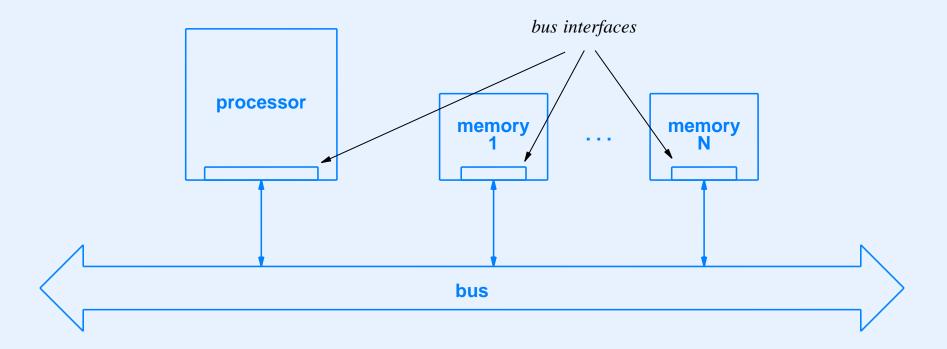

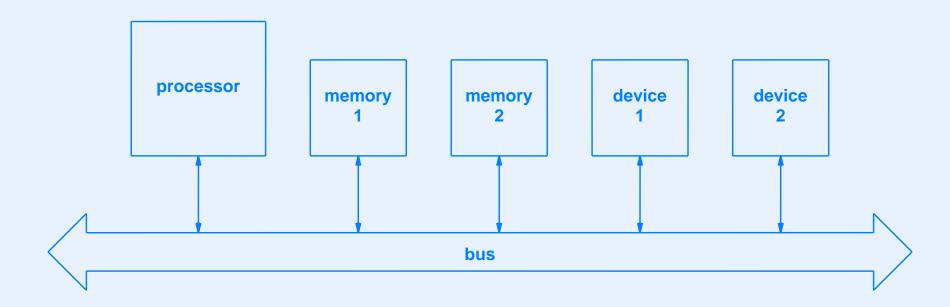

- Buses and bus address spaces

- Role of device drivers

- Advanced topics

- Parallelism and data pipelining

- Power and energy

- Performance and performance assessment

- Architectural hierarchies

### What We Will Not Cover

- The course emphasizes breadth over depth

- Omissions

- Most low-level details (e.g., discussion of electrical properties of resistance, voltage, current and semiconductor physics)

- Quantitative analysis that engineers use to design hardware circuits

- Design rules that specify how logic gates may be interconnected

- Circuit design and design tools

- VLSI chip design and languages such as Verilog

# **Terminology Used With Digital Systems**

- Three key ideas

- Architecture

- Design

- Implementation

#### Architecture

- Refers to the overall organization of a computer system

- Analogous to a blueprint

- Specifies

- Functionality of major components

- Interconnections among components

- Abstracts away details

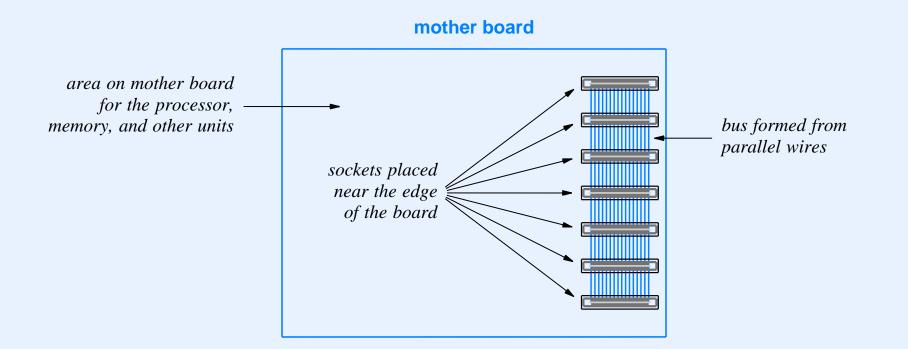

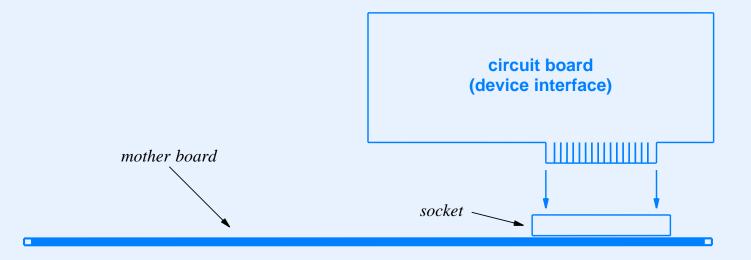

# Design

- Needed before a digital system can be built

- Translates architecture into components

- Fills in details that the architectural specification omits

- Specifies items such as

- How components are grouped onto boards

- How power is distributed to boards

- Many designs can satisfy a given architecture

#### Implementation

- All details necessary to build a system

- Includes

- Specific part numbers to be used

- Mechanical specifications of chassis and cases

- Layout of components on boards

- Power supplies and power distribution

- Signal wiring and connectors

#### Summary

- Architecture is required because understanding computer organization leads to programming excellence

- This course covers the four essential aspects of computer architecture

- Digital logic

- Processors

- Memory

- I/O

- You will have fun with hardware in the lab

# **Questions?**

#### Module II

Fundamentals Of Digital Logic

# **Our Goals**

- Understand the basics

- Concepts

- How computers work at the lowest level

- Avoid whenever possible

- Device physics

- Engineering design rules

- Implementation details

# **Electrical Terminology**

- Voltage

- Quantifiable property of electricity

- Measure of potential force

- Unit of measure: *volt*

- Current

- Quantifiable property of electricity

- Measure of electron flow along a path

- Unit of measure: *ampere (amp)*

# Analogy

- Voltage is analogous to water pressure

- Current is analogous to flowing water

- Can have

- High pressure with little flow

- Large flow with little pressure

# **Measuring Voltage**

- Device used is called *voltmeter*

- Note: can only be measured as *difference* between two points

- We will

- Assume one point represents zero volts (known as ground)

- Express voltage of second point with respect to ground

# **In Practice**

- In lab, chips will operate on five volts

- Two wires connect each chip to *power supply*

- Ground (zero volts)

- Power (five volts)

- Every chip needs power and ground connections

- Notes

- Logic diagrams do not show power and ground

- Raspberry Pi operates on 3.3 volts, so conversion is required to connect the Pi to other chips

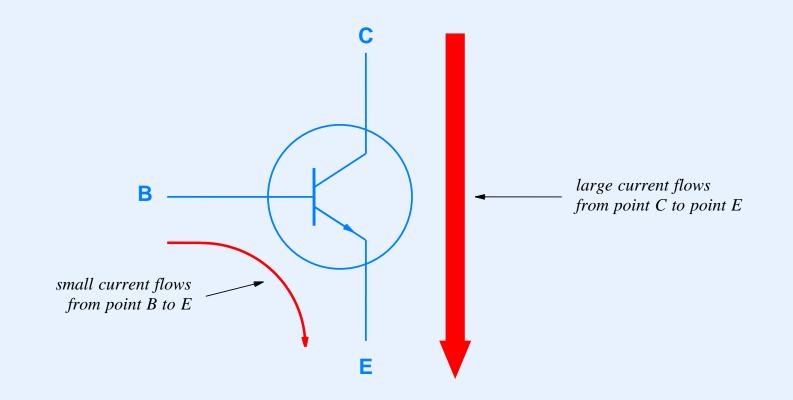

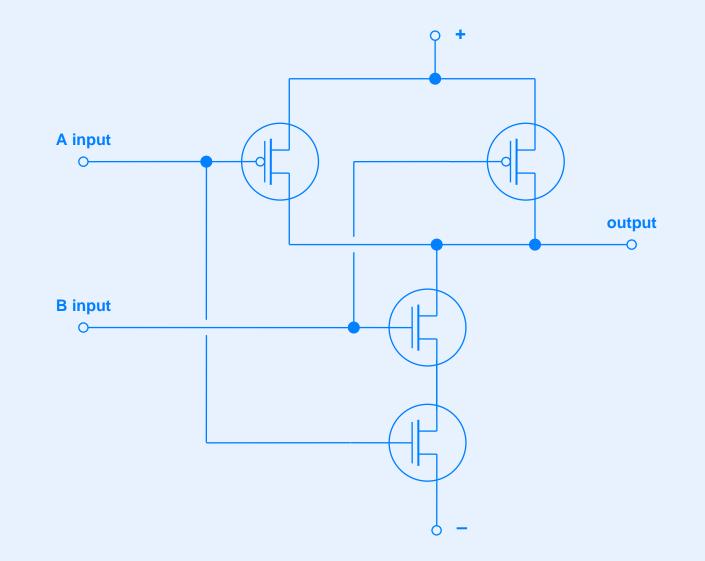

# Transistor

- Basic building block of electronic circuits

- Operates on electrical current

- Traditional transistor

- Has three external connections

- \* Emitter

- \* Base (control)

- \* Collector

- Acts like an *amplifier* a small current between base and emitter controls large current between collector and emitter

#### **Illustration Of A Traditional Transistor**

• Amplification means the large output current varies exactly like the small input current

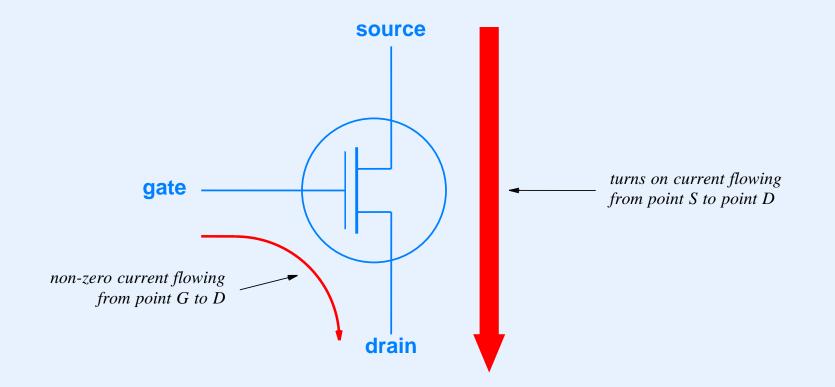

#### **Field Effect Transistor**

- Called a *Metal Oxide Semiconductor FET (MOSFET)* when used on a CMOS chip

- Three external connections

- Source

- Gate

- Drain

- Designed to act as a switch (on or off)

- When the input reaches a threshold (i.e., becomes logic 1), the transistor turns on and passes full current

- When the input falls below a threshold (i.e., becomes logic 0), the transistor turns off and passes no current

# Illustration Of A Field Effect Transistor (Used For Switching)

- Input arrives at the gate

- Logic zero (zero volts) means the transistor is off; logic 1 (positive voltage) turns the transistor on

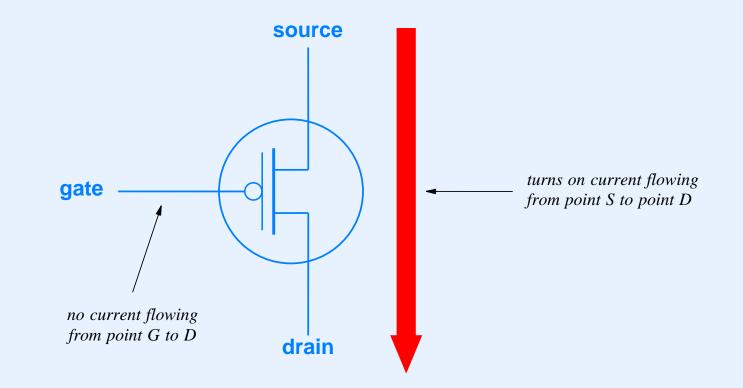

# Alternative Field Effect Transistor (Also Used For Switching)

- Circle on the gate indicates an inversion

- Logic 0 (zero volts) turns the transistor on, and logic 1 (positive voltage) turns the transistor off

## **Boolean Logic**

- Mathematical basis for digital circuits

- Three basic functions: *and*, *or*, and *not*

| Α | В | A and B | Α | В | A or B | Α | not A |

|---|---|---------|---|---|--------|---|-------|

| 0 | 0 | 0       | 0 | 0 | 0      | 0 | 1     |

| 0 | 1 | 0       | 0 | 1 | 1      | 1 | 0     |

| 1 | 0 | 0       | 1 | 0 | 1      |   |       |

| 1 | 1 | 1       | 1 | 1 | 1      |   |       |

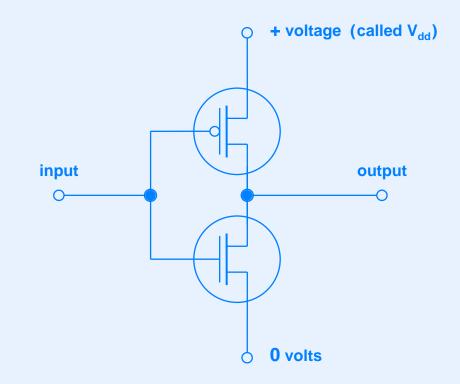

# **Digital Logic**

- Can implement Boolean functions with transistors

- Five volts represents Boolean 1 (true)

- Zero volts represents Boolean 0 (false)

### **Transistors Implementing Boolean Not**

- When input is zero volts, output is connected to + voltage

- When input is five volts, output is connected to 0 volts

- Hardware engineers use  $V_{dd}$  to denote positive voltage

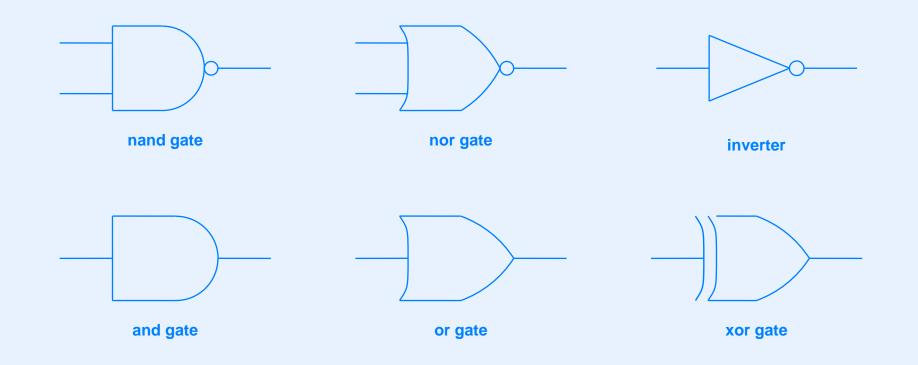

# Logic Gate

- Hardware component

- Consists of integrated circuit

- Implements an individual Boolean function

- To reduce complexity, hardware uses inverse of Boolean functions

- Nand gate implements *not and*

- Nor gate implements not or

- Inverter implements *not*

#### **Truth Tables For Nand, Nor, and Xor Gates**

| Α | В | A nand B | _ | A | В | A nor B | Α | В | A xor B |

|---|---|----------|---|---|---|---------|---|---|---------|

| 0 | 0 | 1        |   | 0 | 0 | 1       | 0 | 0 | 0       |

| 0 | 1 | 1        |   | 0 | 1 | 0       | 0 | 1 | 1       |

| 1 | 0 | 1        |   | 1 | 0 | 0       | 1 | 0 | 1       |

| 1 | 1 | 0        |   | 1 | 1 | 0       | 1 | 1 | 0       |

#### **Example Of Internal Gate Structure (Nand Gate)**

• Solid dot indicates electrical connection

### **Symbols Used In Schematic Diagrams**

• Basic gates

## **Technology For Logic Gates**

- Most popular technology known as *Transistor-Transistor Logic* (*TTL*)

- Allows direct interconnection (a wire can connect output from one gate to input of another)

- Single output can connect to multiple inputs

- Called *fanout*

- Limited to a small number

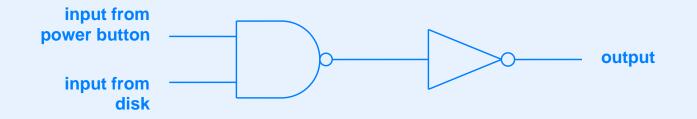

### **Example Interconnection Of TTL Gates**

- Suppose we need a signal to indicate that the power button is depressed and the disk is ready

- Two logic gates are needed to form logical *and*

- Output from nand gate connected to input of inverter

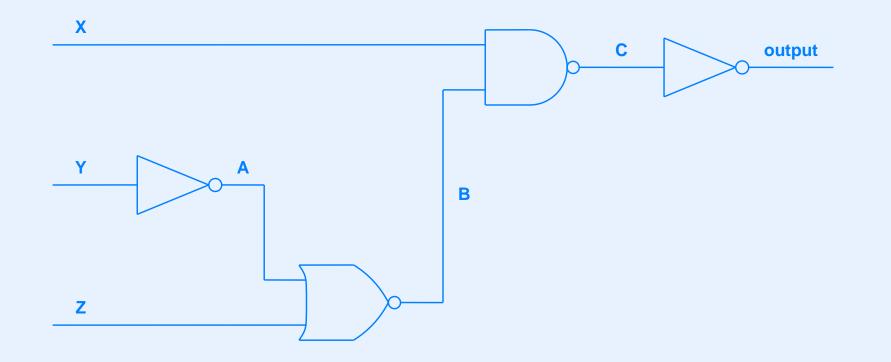

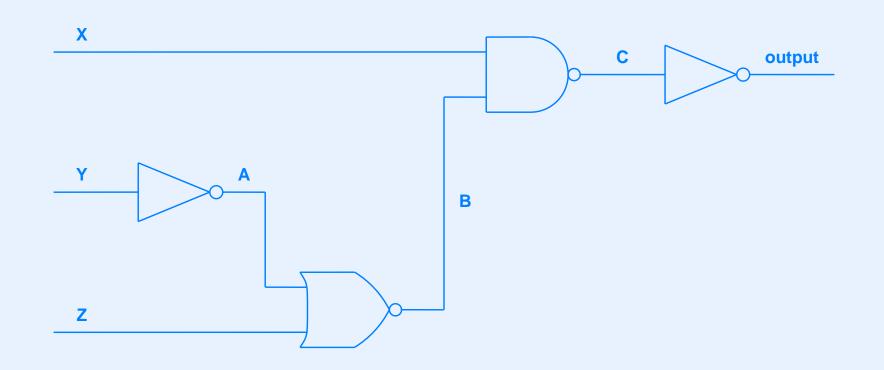

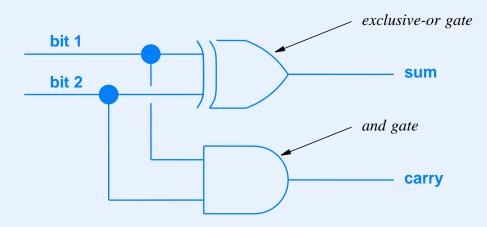

#### **Consider The Following Circuit**

• Question: what does the circuit implement?

# **Two Ways To Describe A Circuit**

- Boolean expression

- Often used when designing circuit

- Can be transformed to equivalent version that requires fewer gates

- Truth table

- Enumerates inputs and outputs

- Often used when debugging a circuit

#### **Describing A Circuit With Boolean Algebra**

- Value at point *A* is: *not Y*

- Value at point *B* is: Z nor (not Y)

#### **Describing A Circuit With Boolean Algebra**

- Value at point *C* is: (X nand ((Z nor (not Y)))

- Value at output is: X and (Z nor (not Y))

# **Simplifying Boolean Expressions**

- Rules are similar to conventional algebra

- Associative

- Reflexive

- Distributive

- See Appendix 2 in the text for details

#### **Describing A Circuit With A Truth Table**

| х | Y | z | А | В | С | output |

|---|---|---|---|---|---|--------|

| 0 | 0 | 0 | 1 | 0 | 1 | 0      |

| 0 | 0 | 1 | 1 | 0 | 1 | 0      |

| 0 | 1 | 0 | 0 | 1 | 1 | 0      |

| 0 | 1 | 1 | 0 | 0 | 1 | 0      |

| 1 | 0 | 0 | 1 | 0 | 1 | 0      |

| 1 | 0 | 1 | 1 | 0 | 1 | 0      |

| 1 | 1 | 0 | 0 | 1 | 0 | 1      |

| 1 | 1 | 1 | 0 | 0 | 1 | 0      |

- Table lists all possible inputs and output for each

- Can also state values for intermediate points

## Nand/Nor Vs. And/Or

- Mathematically, *nand/nor/not* is equivalent to *and/or/not*

- Practically

- It is possible to construct *and* and *or* gates

- Sometimes, humans find *and* and *or* operations easier to understand

- Example circuit or truth table output can be described by Boolean expression:

X and Y and (not Z)

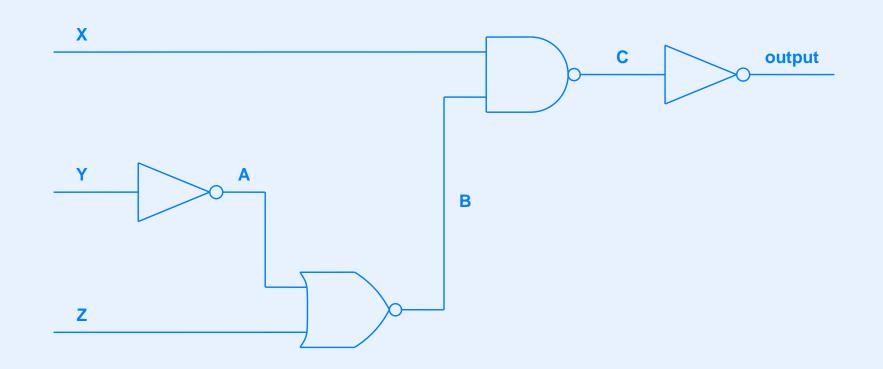

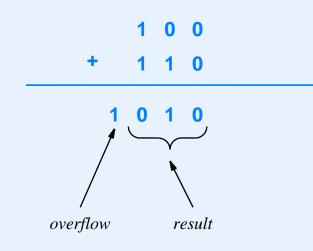

### **Binary Addition**

- How does a computer perform addition?

- Analogous to the method used in elementary school

- Each digit is a single bit

• Note: first bit never has a carry input

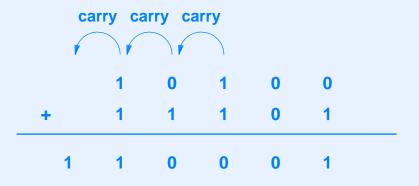

### Half-Adder Circuit

- Adds two input bits

- Produces two output bits

- Sum

- Carry

- We will use *exclusive or* gate plus *and* gate

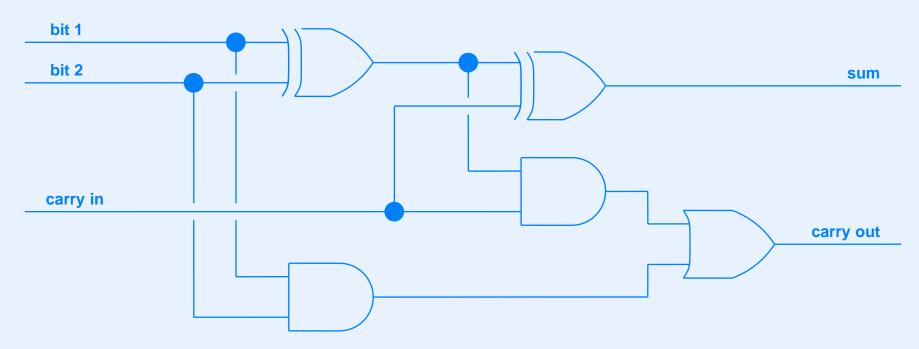

### **Full-Adder Circuit**

- Input is two bits plus a carry

- Produces two output bits

- Sum

- Carry

## **In Practice**

- A single gate only has a few connections

- A chip has many pins for external connections

- Result: package multiple gates on each chip

- We will see examples shortly

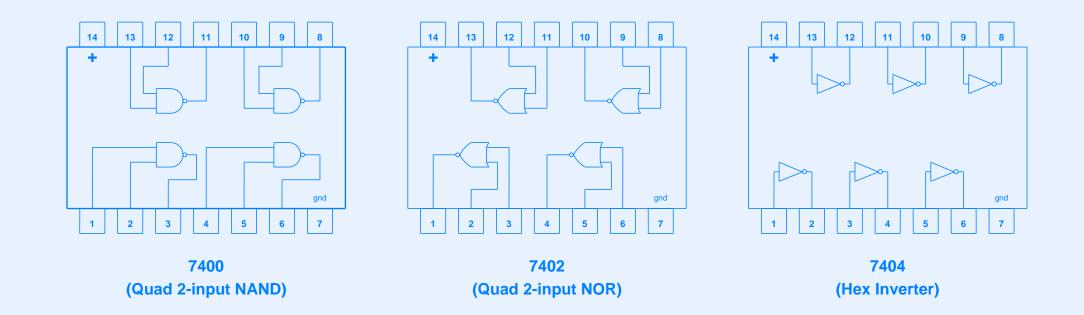

## An Example Logic Gate Technology

- 7400 family of chips

- Package is about one-half inch long

- Implement TTL logic

- Powered by five volts

- Each chip contains multiple gates

### **Example Gates On 7400-Series Chips**

- Pins 7 and 14 connect to ground and power

- Power and ground *must* be connected for the chip to operate

• Question: how can computers be constructed from simple logic gates?

- Question: how can computers be constructed from simple logic gates?

- Answer: they cannot

- Question: how can computers be constructed from simple logic gates?

- Answer: they cannot

- Logic gates only provide a Boolean combination of inputs (known as *combinatorial circuits*)

- Question: how can computers be constructed from simple logic gates?

- Answer: they cannot

- Logic gates only provide a Boolean combination of inputs (known as *combinatorial circuits*)

- Additional functionality is needed

- Circuits that maintain state

- Circuits that operate on a clock

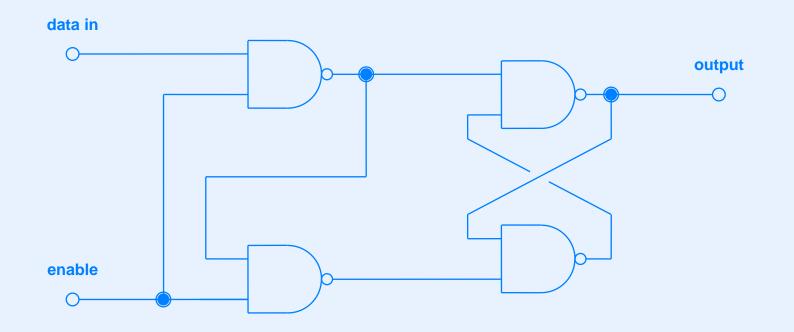

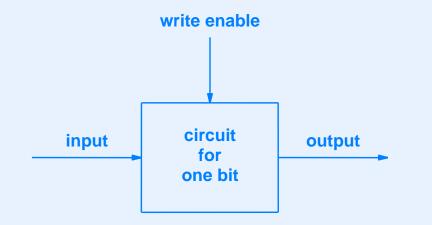

### **Circuits That Maintain State**

- More sophisticated than combinatorial circuits

- Output depends on history of previous input as well as values on input lines

### **Basic Circuit That Maintains State**

- Known as *latch*

- Has two inputs: *data* and *enable*

- When enable is 1, output is same as data

- When enable goes to 0, output stays locked at current value

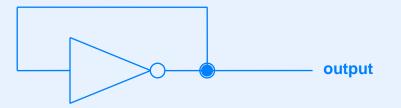

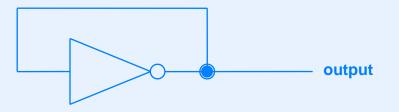

• Key in understanding a latch

- Key in understanding a latch

- Consider the circuit

• What does it do?

- Key in understanding a latch

- Consider the circuit

- What does it do?

- Mathematically, the circuit is meaningless because an inverter produces the complement of its input, but in this case the output is fed back into the input

- Practically, a *propagation delay* means the output stays the same for a short time, and then changes

- Result: output varies over time, 0 for time t, 1 for time t, 0 for time t, and so on, where t is the propagation delay

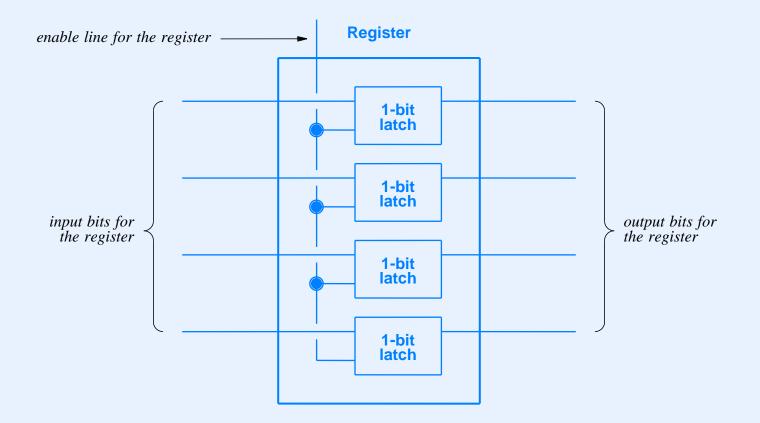

## Register

- Basic building block for a computer

- Acts like a miniature N-bit memory

- Can be built out of latches

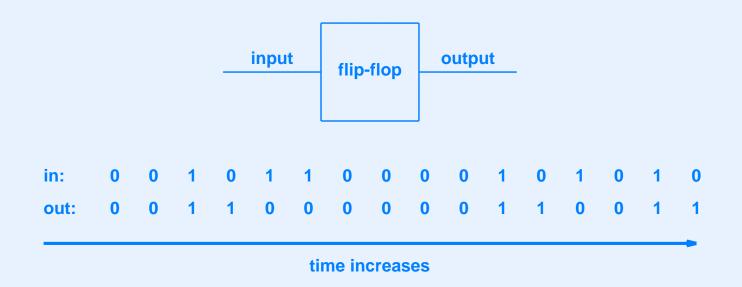

## A More Complex Circuit That Maintains State

- Basic *flip-flop*

- Can be constructed from a pair of latches

- Analogous to push-button power switch (i.e., push-on push-off)

- Each new 1 received as input causes output to reverse

- First input pulse causes flip-flop to turn on

- Second input pulse causes flip-flop to turn off

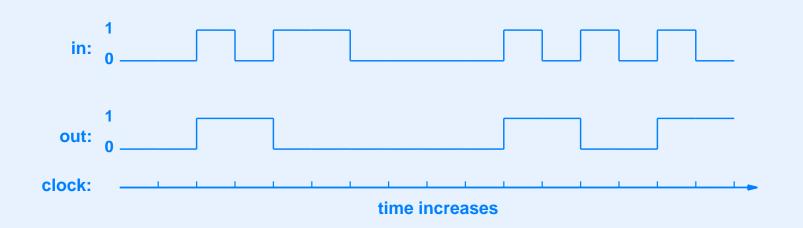

### **Output Of A Flip-Flop**

• Note: output only changes when input makes a transition from zero to one (i.e., *rises*)

### **Flip-Flop Action Plotted As Transition Diagram**

- All changes synchronized with clock (described later)

- Output changes on *rising edge* of input

- Also called *leading edge*

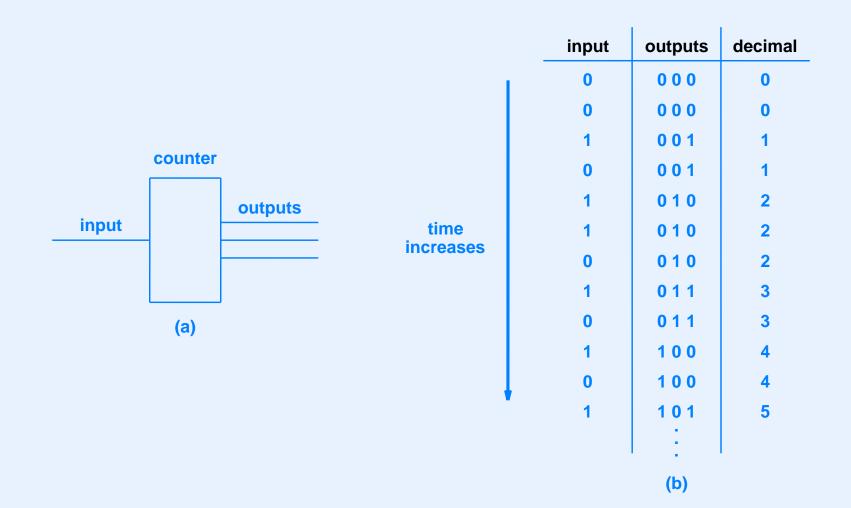

### **Binary Counter**

- Counts input pulses

- Output is binary value

- Includes *reset line* to restart count at zero

- Example: 4-bit counter available as single integrated circuit

## **Illustration Of Counter**

- Part (a) shows the schematic of a counter chip

- Part (b) shows the output as the input changes

Computer Architecture – Module 2

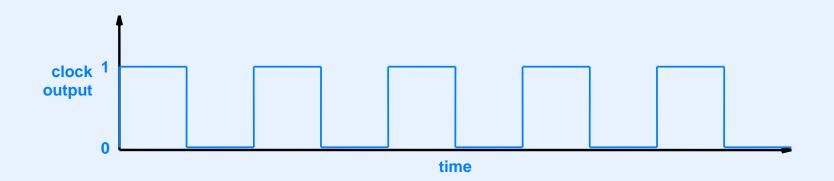

## Clock

- Permits active circuits

- Electronic circuit that pulses regularly

- Measured in cycles per second (Hz)

- Output of clock is *square wave* (sequence of 1 0 1 0 1 ... )

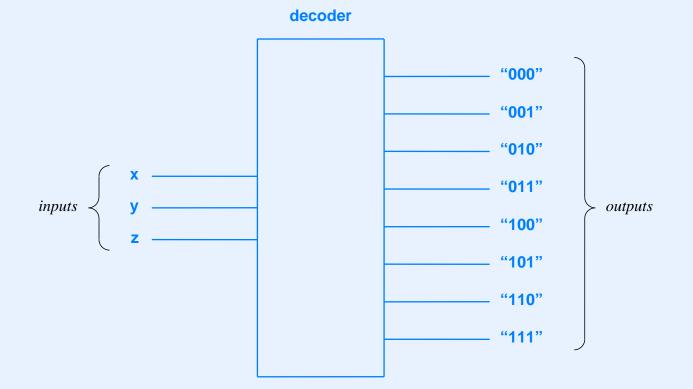

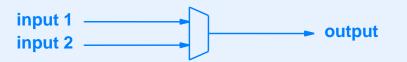

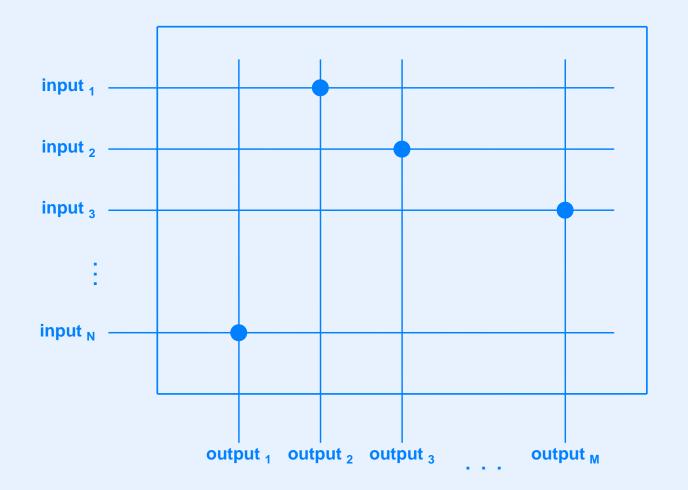

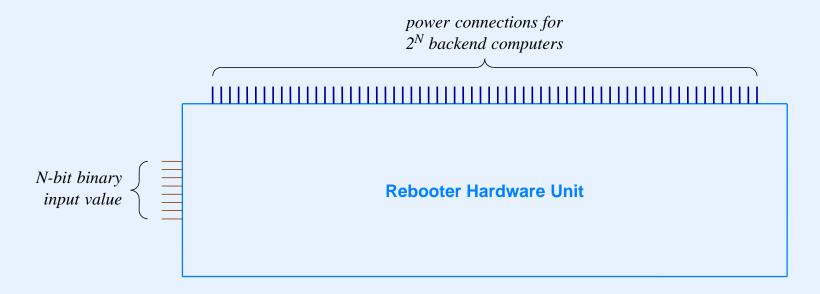

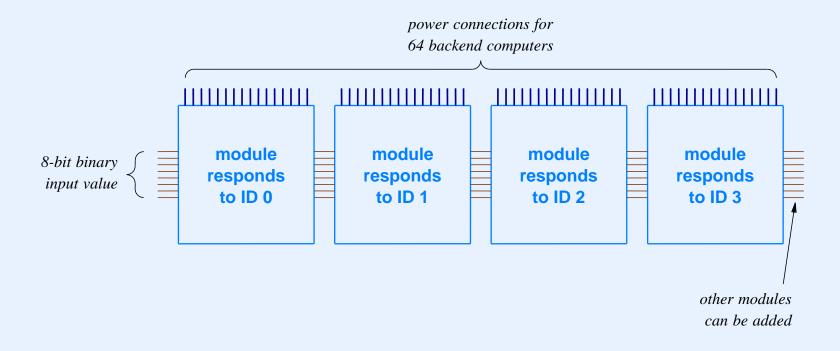

## **Decoder/Demultiplexor**

- Takes binary number as input

- Uses input to select one output

- Technical distinction

- *Decoder* simply selects one of its outputs

- *Demultiplexor* feeds a special input to the selected output

- In practice: engineers often use the term "demux" for either, and blur the distinction

## **Illustration Of Decoder**

• Binary value on input lines determines which output is active

• Technical detail: on some decoder chips, an active output is logic 0 and all others are logic 1

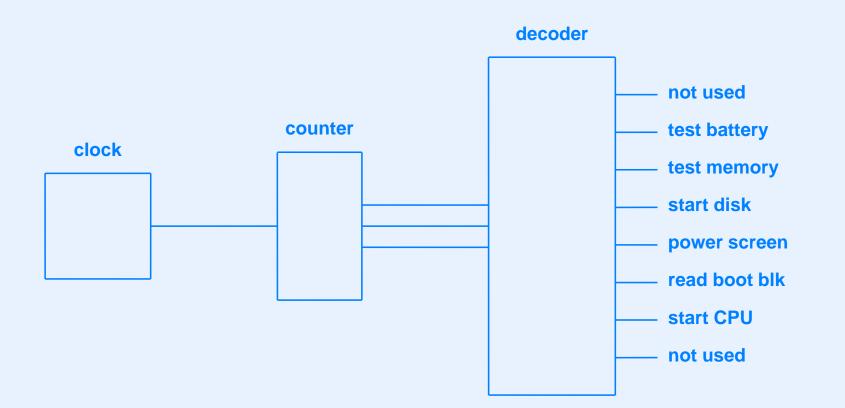

## **Example: Execute A Sequence Of Steps**

- Imagine the power-on sequence for an embedded system

- Test the battery

- Power on and test the memory

- Start the disk

- Power up the display

- Read boot sector from disk into memory

- Start the CPU

- Separate hardware module performs each task

- Need to activate the modules in sequence

Copyright © 2016 by Douglas Comer. All rights reserved

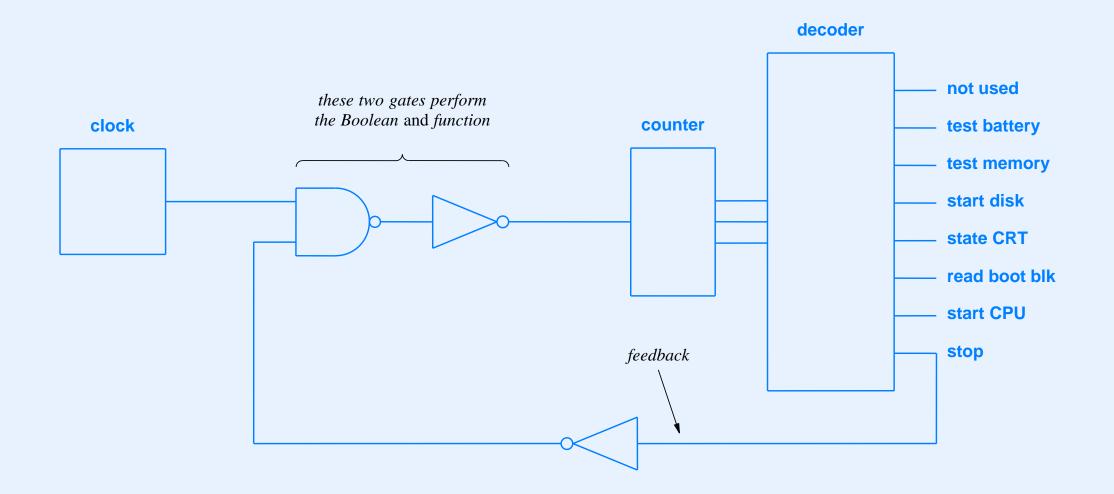

## **Circuit To Execute A Sequence**

- Technique: count clock pulses and use decoder to select an output for each possible counter output

- Note: counter will wrap around to zero, so this is an infinite loop

## Feedback

- Output of circuit used as an input

- Called *feedback*

- Allows more control

- Example: stop sequence when output *F* becomes active

- Boolean algebra

CLOCK and (not F)

## **Illustration Of Feedback For Termination**

• Note additional input needed to restart sequence

## **A Fundamental Difference**

- Software

- Uses iteration

- Software engineers are taught to avoid replicating code

- Iteration increases elegance

- Hardware

- Uses replicated (parallel) hardware units

- Hardware engineers are taught to avoid iterative circuits

- Replication increases performance and reliability

Copyright © 2016 by Douglas Comer. All rights reserved

Fall, 2016

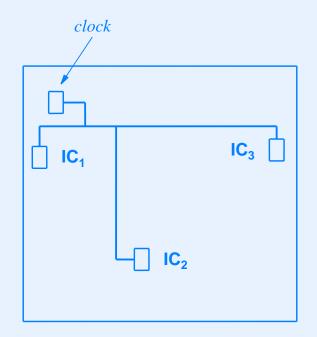

## **Using Spare Gates**

- Note: because chip contains multiple gates, some gates may be unused

- May be possible to reduce total chips needed by employing unused gates

- Example: use a spare nand gate as an inverter by connecting one input to five volts:

1 nand x = not x

• Previous circuit can be implemented with a single chip (a quad 2-input *nand* gate)

## **Practical Engineering Concerns**

- Power consumption (wiring must carry sufficient power)

- Heat dissipation (chips must be kept cool)

- Timing (gates take time to settle after input changes)

- Clock synchronization (clock signal must travel to all chips simultaneously)

- Difference in clock signals (*clock skew*) can cause problems

## **Illustration Of Clock Skew**

• Length of wire determines time required for signal to propagate

## **Clockless Logic**

- Active circuits built without a clock

- Advantages

- Possible power savings

- Avoids clock skew

- Uses two wires to transfer a bit

| Wire 1 | Wire 2 | Meaning                         |

|--------|--------|---------------------------------|

| 0      | 0      | Reset before starting a new bit |

| 0      | 1      | Transfer a 0 bit                |

| 1      | 0      | Transfer a 1 bit                |

| 1      | 1      | Undefined (not used)            |

## **Moore's Law And Classifications**

- Gordon Moore predicted that the number of transistors on a chip would double each year (revised in 1970 to every 18 months)

- Led to the following classifications

| Name                                | Example Use                                       |

|-------------------------------------|---------------------------------------------------|

| Small Scale Integration (SSI)       | The most basic logic such as Boolean gates        |

| Medium Scale Integration (MSI)      | Intermediate logic<br>such as counters            |

| Large Scale Integration (LSI)       | More complex logic such<br>as embedded processors |

| Very Large Scale Integration (VLSI) | The most complex<br>processors (i.e., CPUs)       |

## **Other Terminology Associated With Chips**

- ASIC (Application-Specific Integrated Circuit)

- Custom design for a specific product

- Used when higher speed is needed

- SoC (System on Chip)

- Single IC that contains one or more processors, memories, and I/O device interfaces all interconnected to form a working system

- Used in many low-end devices

## **Levels Of Abstraction**

- Digital systems can be described at various levels of abstraction

- Some examples

| Abstraction   | Implemented With                        |  |  |  |  |  |

|---------------|-----------------------------------------|--|--|--|--|--|

| Computer      | Circuit board(s)                        |  |  |  |  |  |

| Circuit board | Components such as processor and memory |  |  |  |  |  |

| Processor     | VLSI chip                               |  |  |  |  |  |

| VLSI chip     | Many gates                              |  |  |  |  |  |

| Gate          | Many transistors                        |  |  |  |  |  |

| Transistor    | Semiconductor implemented in silicon    |  |  |  |  |  |

## **Reconfigurable Logic**

- Alternative to standard gates

- Allows chip to be configured multiple times

- Can create

- Various gates

- Interconnections

- Typical approach: view a gate as an array and inputs as an index

- Most popular form: *Field Programmable Gate Array (FPGA)*

## **Summary**

- Computer systems are constructed of digital logic circuits

- Fundamental building block is called a *gate*

- Digital circuit can be described by

- Boolean algebra (most useful when designing)

- Truth table (most useful when debugging)

- Clock allows active circuit to perform sequence of operations

- Feedback allows output to control processing

- Practical engineering concerns include

- Power consumption and heat dissipation

- Clock skew and synchronization

# **Questions?**

## Module III

Data And Program Representation

## **Digital Logic**

- Built on two-valued logic system

- Can be interpreted as

- *Positive voltage* and *zero volts*

- *High* and *low*

- *True* and *false*

- Asserted and not asserted

- Underneath, it's all just electrons and wires

## **Data Representation**

- Builds on digital logic

- Applies familiar abstractions

- Interprets sets of Boolean values as

- Numbers

- Characters

- Addresses

- Underneath, it's all just bits

## **Bit (Binary Digit)**

- Direct representation of digital logic values

- Assigned mathematical interpretation

- 0 and 1

- Multiple bits used to represent complex data item

- The same underlying hardware can represent bits of an integer or bits of a character

## Byte

- Set of multiple bits

- Size depends on computer

- Examples of byte sizes

- CDC: 6-bit byte

- BBN: 10-bit byte

- IBM: 8-bit byte

- On most computers, the byte is the smallest addressable unit of storage

- Note: following modern convention, we will assume an 8-bit byte

## **Byte Size And Values**

- Number of bits per byte determines range of values that can be stored

- Byte of k bits can store  $2^k$  values

- Examples

- Six-bit byte can store 64 possible values

- Eight-bit byte can store 256 possible values

## **Binary Representation**

- Bits themselves have no intrinsic meaning

- Byte merely stores string of 0's and 1's

- Example: all possible combinations of three bits

| 000 | 010 | 100 | 110 |

|-----|-----|-----|-----|

| 001 | 011 | 101 | 111 |

• All meaning is determined by how bits are interpreted

## **Two Possible Interpretations Of Three Bits**

- Device status

- First bit has the value 1 if a disk is connected

- Second bit has the value 1 if a printer is connected

- Third bit has the value 1 if a keyboard is connected

- Integer interpretation

- Positional representation uses base 2

- Values are 0 through 7

- We must specify order of bits

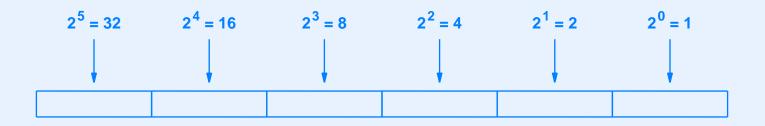

## **Binary Weighted Positional Interpretation**

• Example

010101

is interpreted as

$$0 \times 2^{5} + 1 \times 2^{4} + 0 \times 2^{3} + 1 \times 2^{2} + 0 \times 2^{1} + 1 \times 2^{0} = 21$$

• A set of k bits can represent integers 0 through  $2^{k}-1$

## **Powers Of Two**

| Power Of 2 | <b>Decimal Value</b> | <b>Decimal Digits</b> |  |  |  |

|------------|----------------------|-----------------------|--|--|--|

| 0          | 1                    | 1                     |  |  |  |

| 1          | 2                    | 1                     |  |  |  |

| 2          | 4                    | 1                     |  |  |  |

| 3          | 8                    | 1                     |  |  |  |

| 4          | 16                   | 2                     |  |  |  |

| 5          | 32                   | 2                     |  |  |  |

| 6          | 64                   | 2                     |  |  |  |

| 7          | 128                  | 3                     |  |  |  |

| 8          | 256                  | 3                     |  |  |  |

| 9          | 512                  | 3                     |  |  |  |

| 10         | 1024                 | 4                     |  |  |  |

| 11         | 2048                 | 4                     |  |  |  |

| 12         | 4096                 | 4                     |  |  |  |

| 15         | 16384                | 5                     |  |  |  |

| 16         | 32768                | 5                     |  |  |  |

| 20         | 1048576              | 7                     |  |  |  |

| 30         | 1073741824           | 10                    |  |  |  |

| 32         | 4294967296           | 10                    |  |  |  |

| 64         | 18446744073709551616 | 20                    |  |  |  |

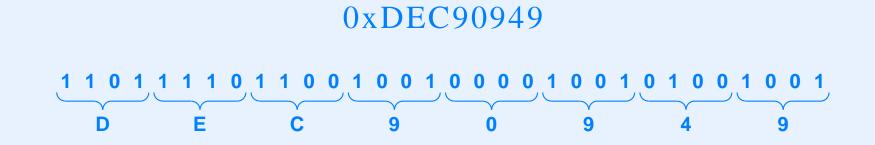

## **Review: Hexadecimal Notation**

- Mathematically, it's base 16

- Practically, it's easier to write than binary

- Each hex digit encodes four bits

| Hex | Binary | Decimal | Hex | Binary | Decimal |

|-----|--------|---------|-----|--------|---------|

| 0   | 0000   | 0       | 8   | 1000   | 8       |

| 1   | 0001   | 1       | 9   | 1001   | 9       |

| 2   | 0010   | 2       | Α   | 1010   | 10      |

| 3   | 0011   | 3       | В   | 1011   | 11      |

| 4   | 0100   | 4       | С   | 1100   | 12      |

| 5   | 0101   | 5       | D   | 1101   | 13      |

| 6   | 0110   | 6       | E   | 1110   | 14      |

| 7   | 0111   | 7       | F   | 1111   | 15      |

• Note: hexadecimal merely represents bits

## **Hexadecimal Constants**

- Supported in some programming languages

- Typical syntax: constant begins with Ox

- Example

## **Character Sets**

- Symbols for upper and lower case letters, digits, and punctuation marks

- Set of symbols defined by computer system

- Each symbol assigned unique bit pattern

- Typically, character set size determined by byte size

- Various character sets have been used in commercial computers

- EBCDIC

- ASCII

- Unicode

## **EBCDIC**

- Extended Binary Coded Decimal Interchange Code

- Defined by IBM

- Popular in 1960s

- Still used on IBM mainframe computers

- Specifies 128 characters

- Example encoding: lower case letter *a* assigned binary value

1000001

## ASCII

- American Standard Code for Information Interchange

- Vendor independent: defined by American National Standards Institute (ANSI)

- Adopted by PC manufacturers

- Specifies 128 characters

- Example encoding: lower case letter *a* assigned binary value

#### 01100001

• Unprintable characters used for modem control

## **Full ASCII Character Set**

| 00 | nul | 01 | soh | 02         | stx | 03        | etx | 04        | eot | 05        | enq | 06         | ack | 07         | bel |

|----|-----|----|-----|------------|-----|-----------|-----|-----------|-----|-----------|-----|------------|-----|------------|-----|

| 08 | bs  | 09 | ht  | <b>0</b> A | lf  | <b>0B</b> | vt  | <b>0C</b> | np  | <b>0D</b> | cr  | <b>0E</b>  | SO  | 0F         | si  |

| 10 | dle | 11 | dc1 | 12         | dc2 | 13        | dc3 | 14        | dc4 | 15        | nak | 16         | syn | 17         | etb |

| 18 | can | 19 | em  | 1A         | sub | 1B        | esc | 1C        | fs  | 1D        | gs  | 1e         | rs  | 1F         | us  |

| 20 | sp  | 21 | 1   | 22         | н   | 23        | #   | 24        | \$  | 25        | %   | 26         | &   | 27         | ,   |

| 28 | (   | 29 | )   | <b>2A</b>  | *   | 2B        | +   | 2C        | ,   | <b>2D</b> | -   | <b>2E</b>  | 1.1 | 2F         | 1   |

| 30 | 0   | 31 | 1   | 32         | 2   | 33        | 3   | 34        | 4   | 35        | 5   | 36         | 6   | 37         | 7   |

| 38 | 8   | 39 | 9   | <b>3A</b>  | 1   | 3B        | ;   | <b>3C</b> | <   | 3D        | =   | 3E         | >   | 3F         | ?   |

| 40 | @   | 41 | Α   | 42         | В   | 43        | С   | 44        | D   | 45        | Е   | 46         | F   | 47         | G   |

| 48 | н   | 49 | 1.1 | <b>4</b> A | J   | <b>4B</b> | K   | <b>4C</b> | L.  | <b>4D</b> | Μ   | <b>4E</b>  | Ν   | 4F         | Ο   |

| 50 | Ρ   | 51 | Q   | 52         | R   | 53        | S   | 54        | т   | 55        | U   | <b>56</b>  | V   | 57         | W   |

| 58 | X   | 59 | Υ   | <b>5A</b>  | Z   | 5B        | T   | <b>5C</b> | A - | <b>5D</b> | 1   | <b>5E</b>  | ۸   | 5F         | _   |

| 60 | 4   | 61 | а   | 62         | b   | <b>63</b> | С   | 64        | d   | <b>65</b> | е   | 66         | f   | 67         | g   |

| 68 | h   | 69 | i   | 6A         | j   | 6B        | k   | 6C        | 1   | 6D        | m   | 6 <b>E</b> | n   | 6 <b>F</b> | ο   |

| 70 | р   | 71 | q   | 72         | r   | 73        | S   | 74        | t   | 75        | u   | 76         | v   | 77         | w   |

| 78 | X   | 79 | у   | <b>7</b> A | z   | <b>7B</b> | {   | 7C        |     | <b>7D</b> | }   | <b>7E</b>  | ~   | <b>7F</b>  | del |

## Unicode

- Extends ASCII

- Assigns meaning to values from 128 through 255

- Character can be 16 bits long

- Advantage: can represent larger set of characters

- Motivation: accommodate languages such as Chinese

#### **Integer Representation In Binary**

- Each binary integer represented in k bits

- Computers have used k = 8, 16, 32, 60, and 64

- Many computers support multiple integer sizes (e.g., 16, 32, and 64 bit integers)

- 2<sup>k</sup> possible bit combinations exist for k bits

- Positional interpretation produces *unsigned integers*

## **Unsigned Integers**

- Straightforward positional interpretation

- Each successive bit represents next power of 2

- No provision for negative values

- Precision is fixed (size of integers is a constant)

- Arithmetic operations can produce *overflow* or *underflow* (result cannot be represented in *k* bits)

- Overflow handled with *wraparound* and *carry bit*

#### **Illustration Of Overflow**

- Values wrap around address space

- Hardware records overflow in separate carry indicator

- Software must test after arithmetic operation

- Can be used to raise an *exception*

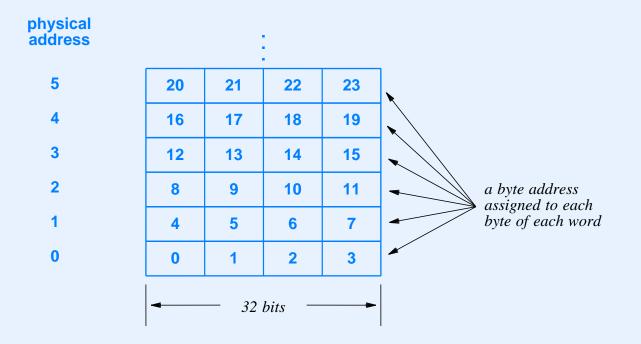

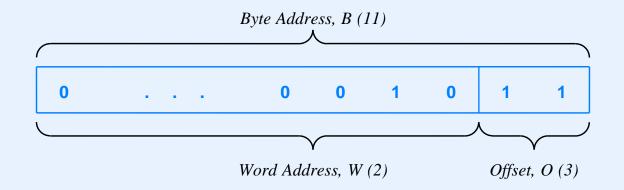

# **Numbering Bits And Bytes**

- Need to choose order for

- Storage in physical memory system

- Transmission over a data network

- Bit order

- Handled by hardware

- Usually hidden from programmer

- Byte order

- Affects multi-byte data items such as integers

- Visible and important to programmer

## **Integer Byte Order**

- *Little Endian* places least significant byte of integer in lowest memory location

- *Big Endian* places most significant byte of integer in lowest memory location

Interesting historical variation: Digital Equipment Corporation once used an ordering with 32-bit integers divided into sixteen-bit words in big endian order and bytes within the words in little endian order.

### **Illustration Of Big And Little Endian Byte Order**

#### 00011101 10100010 00111011 01100111

(a) Integer 497,171,303 in binary positional representation

| <br>loc. i   | <i>loc. i</i> +1 | <i>loc. i</i> +2 | <i>loc. i</i> +3 |  |

|--------------|------------------|------------------|------------------|--|

| <br>01100111 | 00111011         | 10100010         | 00011101         |  |

(b) The integer stored in little endian order

| <br>loc. i   | <i>loc. i</i> +1 | <i>loc. i</i> +2 | <i>loc. i</i> +3 |  |

|--------------|------------------|------------------|------------------|--|

| <br>00011101 | 10100010         | 00111011         | 01100111         |  |

(c) The integer stored in big endian order

• Note: difference is especially important when transferring data over the Internet between computers for which the byte ordering differs

# **Signed Binary Integers**

- Signed arithmetic is needed by most programs

- Several representations are possible

- Each has been used in at least one computer

- Some bit patterns are used for negative values (typically half)

- Tradeoff: unsigned representation cannot store negative values, but can store integers that are twice as large as a signed representation

# **Signed Integer Representations**

- Three signed representations have been used

- Sign magnitude

- One's complement

- Two's complement

- Each has interesting quirks

# **Sign Magnitude Representation**

- Familiar to humans

- First bit represents sign

- Successive bits represent absolute value of integer

- Interesting quirk: can create negative zero

# **One's Complement Representation**

- Positive number uses positional representation

- Negative number formed by inverting all bits of positive value

- Example of 4-bit one's complement

- 0010 represents 2

- -1101 represents -2

- Interesting quirk: two representations for zero (all 0's and all 1's)

- Note: Internet checksum uses one's complement

# **Two's Complement Representation**

- Positive number uses positional representation

- Negative number formed by subtracting 1 from positive value and inverting all bits of result

- Example of 4-bit two's complement

- 0010 represents 2

- -1110 represents -2

- High-order bit is set if number is negative

- Interesting quirk: one more negative value than positive values

# Implementation Of Unsigned And Two's Complement

- We consider unsigned and two's complement together because

- A single piece of hardware can handle both unsigned and two's complement integer arithmetic

- Software can choose an interpretation for each integer

- Example using 4 bits

- Adding 1 to binary 1001 produces 1010

- Unsigned interpretation goes from 9 to 10

- Two's complement interpretation goes from -7 to -6

#### **Example Of Signed Representation (4 bit integers)**

| Binary<br>String | Unsigned<br>(positional)<br>Interpretation | Sign<br>Magnitude<br>Interpretation | One's<br>Complement<br>Interpretation | Two's<br>Complement<br>Interpretation |

|------------------|--------------------------------------------|-------------------------------------|---------------------------------------|---------------------------------------|

| 0000             | 0                                          | 0                                   | 0                                     | 0                                     |

| 0001             | 1                                          | 1                                   | 1                                     | 1                                     |

| 0010             | 2                                          | 2                                   | 2                                     | 2                                     |

| 0011             | 3                                          | 3                                   | 3                                     | 3                                     |

| 0100             | 4                                          | 4                                   | 4                                     | 4                                     |

| 0101             | 5                                          | 5                                   | 5                                     | 5                                     |

| 0110             | 6                                          | 6                                   | 6                                     | 6                                     |

| 0111             | 7                                          | 7                                   | 7                                     | 7                                     |

| 1000             | 8                                          | -0                                  | -7                                    | -8                                    |

| 1001             | 9                                          | -1                                  | -6                                    | -7                                    |

| 1010             | 10                                         | -2                                  | -5                                    | -6                                    |

| 1011             | 11                                         | -3                                  | -4                                    | -5                                    |

| 1100             | 12                                         | -4                                  | -3                                    | -4                                    |

| 1101             | 13                                         | -5                                  | -2                                    | -3                                    |

| 1110             | 14                                         | -6                                  | -1                                    | -2                                    |

| 1111             | 15                                         | -7                                  | -0                                    | -1                                    |

### **Sign Extension**

- Needed for unsigned and two's complement representations

- Used to accommodate multiple sizes of integers

- Extends high-order bit (known as *sign bit*)

# **Explanation Of Sign Extension**

- Assume computer

- Supports 32-bit and 64-bit integers

- Uses two's complement representation

- When 32-bit integer assigned to 64-bit integer, correct numeric value requires upper 32 bits to be filled with

- Zeroes for a positive number

- Ones for a negative number

- In essence, high-order (sign) bit from the 32-bit integer must be replicated to fill high-order bits of larger integer

#### **Example Of Sign Extension During Assignment**

• The 8-bit version of integer -3 is

#### $1 \ 1 \ 1 \ 1 \ 1 \ 1 \ 0 \ 1$

• The 16-bit version of integer –3 is

#### 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 1 replicated

• During assignment to a larger integer, hardware copies all bits of smaller integer and then replicates the high-order (sign) bit in remaining bits

### **Summary Of Sign Extension**

Sign extension: in two's complement arithmetic, when an integer Q composed of K bits is copied to an integer of more than K bits, the additional high-order bits are set equal to the top bit of Q. Extending the sign bit means the numeric value remains the same.

# **Sign Extension During Shift**

- Right shift of a negative value should produce a negative value

- Example

- Shifting -4 one bit should produce -2 (divide by 2)

- Using sixteen-bit representation, –4 is:

1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0

• After right shift of one bit, value is -2:

1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0

• Solution: replicate high-order bit during right shift

# **A Consequence For Programmers**

- Most computers use two's complement hardware, which performs sign extension

- Same hardware is used for unsigned arithmetic, which means that assigning an unsigned integer to a larger unsigned integer can change the value

- To prevent errors from occurring, a programmer or a compiler must add code to mask off the extended sign bits

- Example code

#### **Binary Coded Decimal**

- Pioneered by IBM

- Represents integer as a string of digits

- Unpacked: one digit per 8-bit byte

- Packed: one digit per 4-bit nibble

- Uses sign-magnitude representation

- Example of unpacked BCD

- Integer 123456 is stored as

- 0x01 0x02 0x03 0x04 0x05 0x06

- Integer –123456 is stored as:

- 0x01 0x02 0x03 0x04 0x05 0x06 0x0D

#### **Assessment Of Binary Coded Decimal**

- Disadvantages:

- Take more space

- Hardware is slower than integer or floating point

- Advantages:

- Gives results humans expect (compare to Excel)

- Avoids repeating binary value for .01

- Preferred by banks

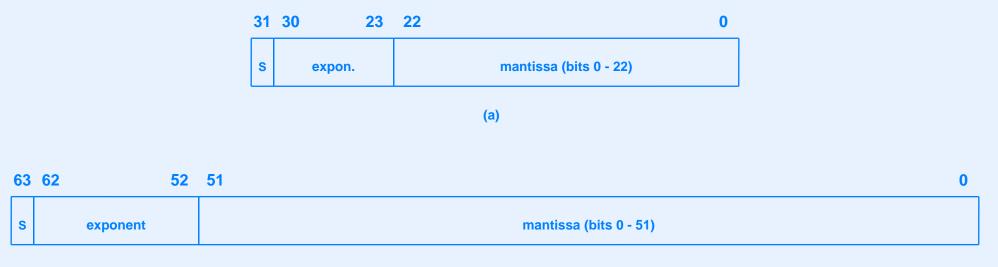

# **Floating Point**

- Fundamental idea: follow standard scientific representation that specifies a few significant digits and an order of magnitude

- Example: Avogadro's number

$6.022 \times 10^{23}$

- Hardware

- Uses base 2 instead of base 10

- Allocates fixed-size bit strings for

- \* Exponent

- \* Mantissa

# **Optimizing Floating Point**

- Mantissa

- *Normalized* to eliminate leading zeroes

- No need to store most significant bit because it is always 1

- Zero is a special case

- Exponent

- Allows negative as well as positive values

- Biased to permit rapid magnitude comparison

#### **Example Floating Point Representation: IEEE Standard 754**

- Specifies single-precision and double-precision representations

- Widely adopted by computer architects

**(b)**

# **Special Values In IEEE Floating Point**

- Zero

- Positive infinity

- Negative infinity

- Note: infinity values handle cases such as the result of dividing by zero

#### **Range Of Values In IEEE Floating Point**

• The single precision range is

$2^{-126}$  to  $2^{127}$

• The decimal equivalent is approximately

$10^{-38}$  to  $10^{38}$

#### Range Of Values In IEEE Floating Point (continued)

• The double precision range is enormously larger than single precision

$2^{-1022}$  to  $2^{1023}$

• The decimal equivalent is approximately

$10^{-308}$  to  $10^{308}$

#### **An Example Floating Point Value**

- Consider the decimal value 6.5

- In binary, 6 is 110 and .5 is .1, giving 110.1

- Normalizing gives  $1.101 \times 2^2$

- In IEEE floating point

- The sign bit is zero (for a positive number)

- The exponent is biased by adding 127, giving 129 (10000001 in binary)

- The leading 1 of the mantissa is not stored, giving (10100000...0 in binary)

- The resulting binary value is

| S | exponent (23 – 30) | mantissa (bits 0 – 22)                  |  |  |

|---|--------------------|-----------------------------------------|--|--|

| 0 | 1000001            | 1 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 |  |  |

## **Data Aggregates**

- Typically arranged in contiguous memory

- Example: struct with three integers

| 0          | 1 | 2          | 3 | 4          | 5 |

|------------|---|------------|---|------------|---|

|            |   |            |   |            |   |

| integer #1 |   | integer #2 |   | integer #3 |   |

|            |   |            |   |            |   |

• More details later in the course

#### **Summary**

- Fundamental value in digital logic is a bit

- Bits grouped into sets to represent

- Integers

- Characters

- Floating point values

- Integers can be represented as

- Sign magnitude

- One's complement

- Two's complement

#### **Summary**

- One piece of hardware can be used for both

- Two's complement arithmetic

- Unsigned arithmetic

- Bytes of integer can be numbered in

- Big-endian order

- Little-endian order

- Organizations such as ANSI and IEEE define standards for data representation

# **Questions?**

# Module IV

#### **Processors**

# Terminology

- The terms *processor* and *computational engine* refer broadly to any mechanism that drives computation

- Wide variety of sizes and complexity

- Processor is key element in all computational systems

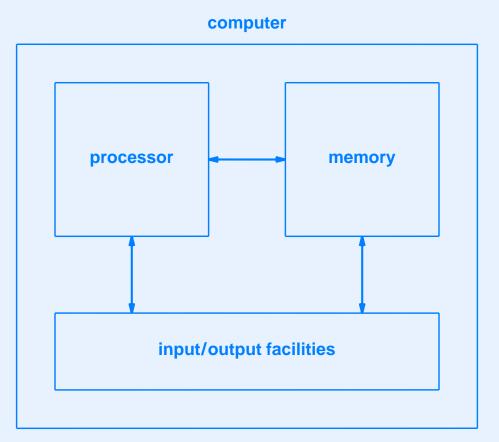

#### **Von Neumann Architecture**

- Characteristic of most modern processors

- Reference to mathematician John Von Neumann, a pioneer in computer architecture

- Unlike *Harvard architecture*, there is one memory

- Fundamental concept is a *stored program* (i.e., a program in the same memory as the data)

- Three basic components interact to form a computational system

- Processor

- Memory

- I/O facilities

#### **Illustration Of Von Neumann Architecture**

#### Processor

- Digital device

- Performs computation involving multiple steps

- Wide variety of capabilities

- Mechanisms available

- Fixed logic

- Selectable logic

- Parameterized logic

- Programmable logic

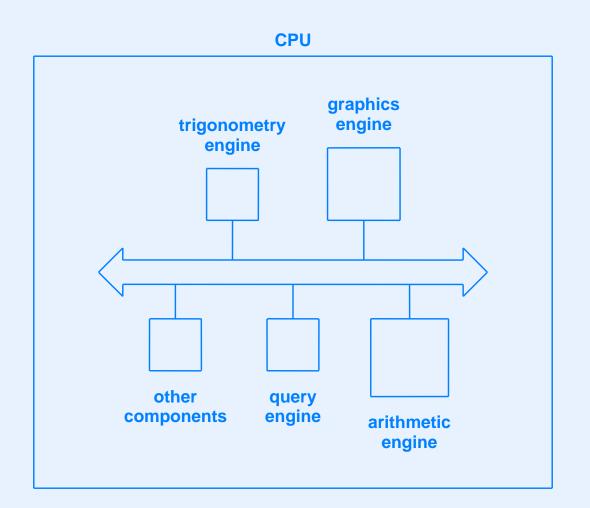

# **Hierarchical Structure And Processors**

- Most computer architecture follows a hierarchical approach

- Subparts of a large, central processor are sophisticated enough to meet our definition of processor

- Some engineers use term *computational engine* for subpiece that is less powerful than main processor

#### **Illustration Of Processor Hierarchy**

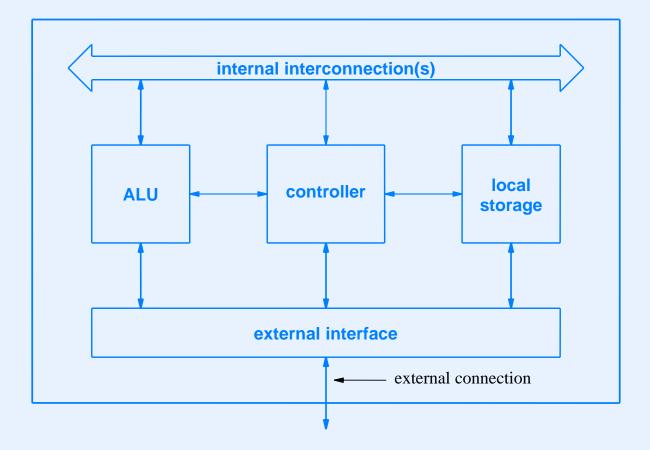

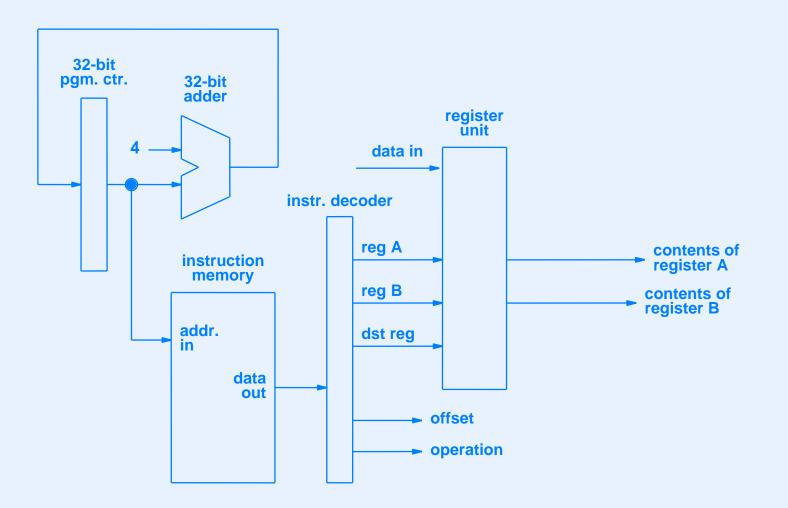

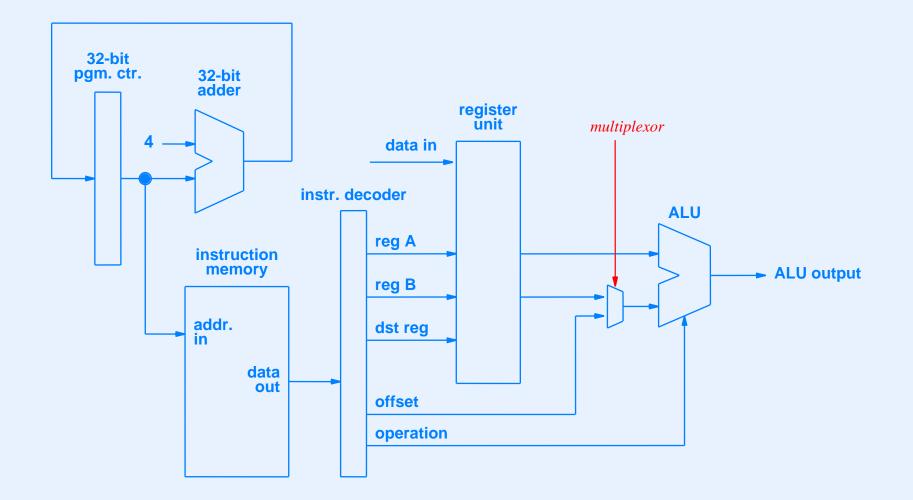

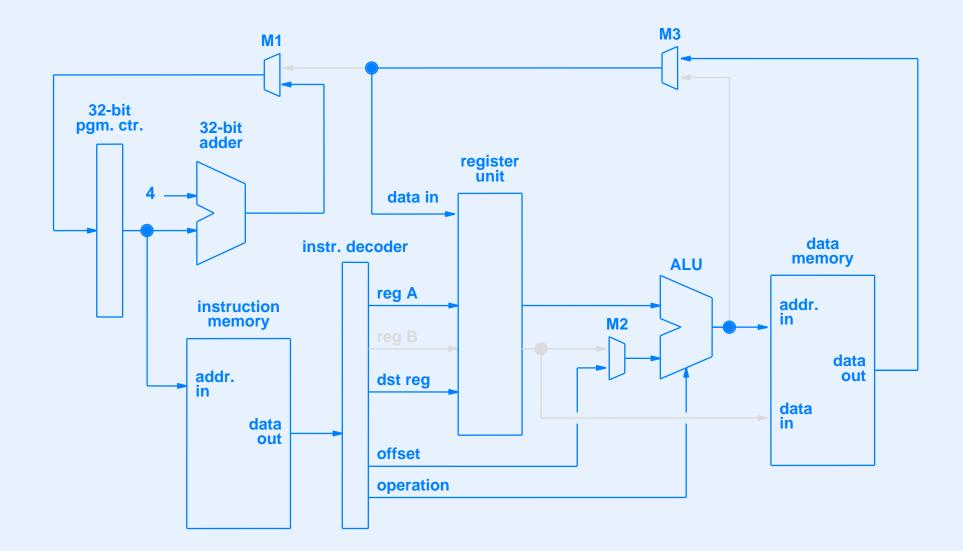

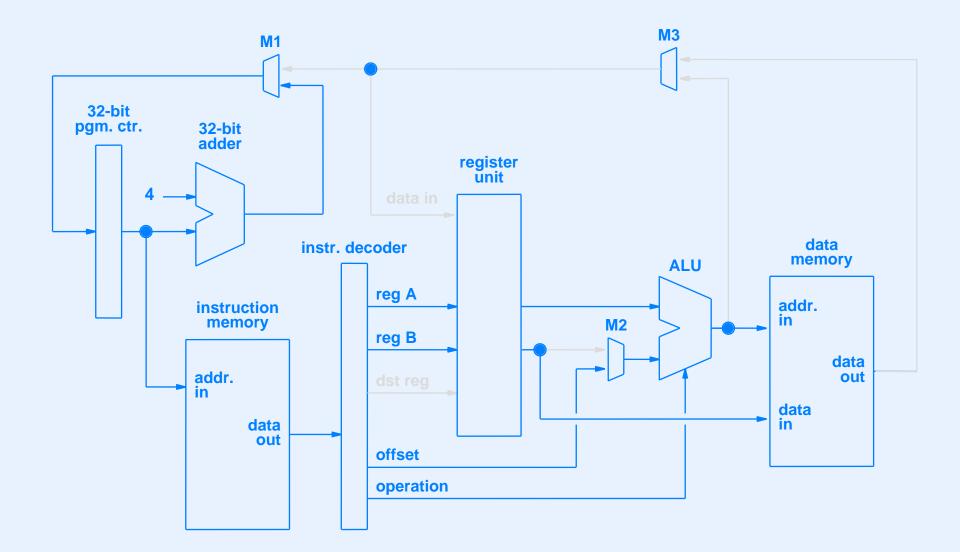

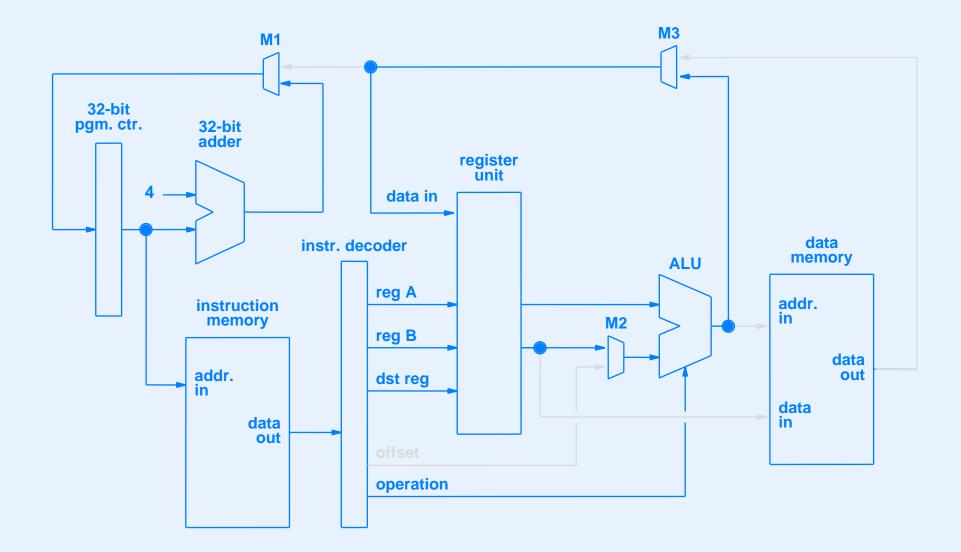

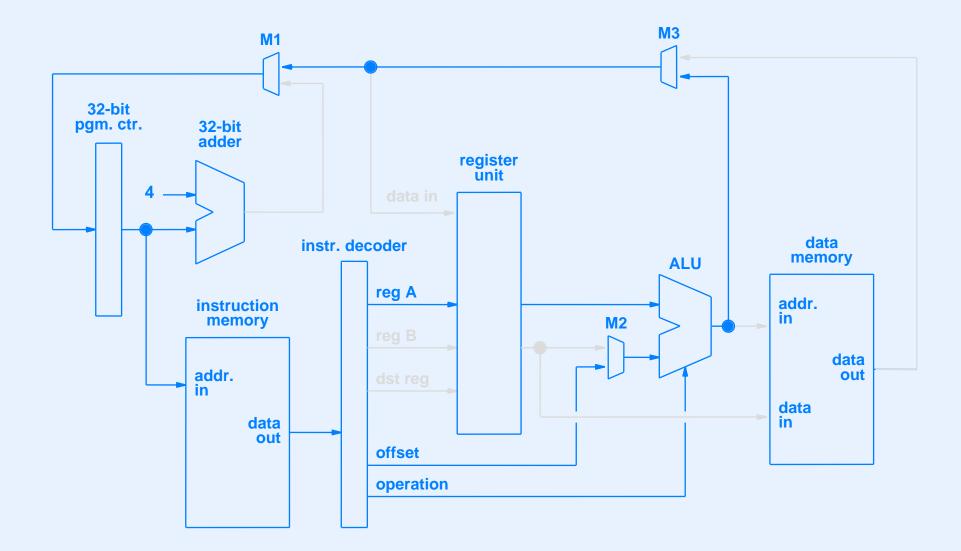

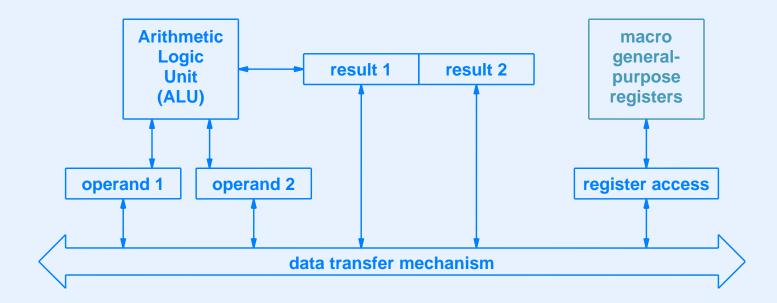

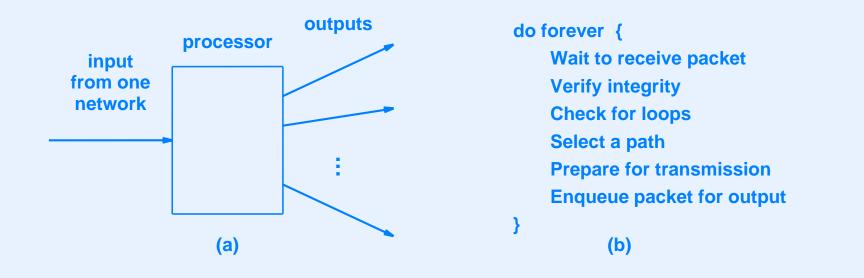

# **Major Components Of A Conventional Processor**

- Controller to coordinate operation (often omitted from architecture diagrams)

- Arithmetic Logic Unit (ALU)

- Local data storage

- Internal interconnections

- External interfaces (I/O buses)

#### **Illustration Of A Conventional Processor**

# **Parts Of A Conventional Processor**

- Controller

- Overall responsibility for execution

- Moves through sequence of steps

- Coordinates other units

- Timing-based operation: knows how long each unit requires and schedules steps accordingly

- Arithmetic Logic Unit

- Operates as directed by controller

- Provides arithmetic and Boolean operations

- Performs one operation at a time as directed

# Parts Of A Conventional Processor (continued)

- Internal interconnections

- Allow transfer of values among units of the processor

- Also called *data paths*

- External interface

- Handles communication between processor and rest of computer system

- Provides interaction with external memory as well as external I/O devices

# Parts Of A Conventional Processor (continued)

- Local data storage

- Holds data values for operations

- Values must be inserted (e.g., loaded from memory) before the operation can be performed

- Typically implemented with *registers*

# **Arithmetic Logic Unit**

- Main computational engine in conventional processor

- Complex unit that can perform variety of tasks

- Typical ALU operations

- Arithmetic (integer add, subtract, multiply, divide)

- Shift (left, right, circular)

- Boolean (and, or, not, exclusive or)

# **Processor Categories And Roles**

- Many possible roles for individual processors in

- Coprocessors

- Microcontrollers

- Embedded system processors

- General-purpose processors

## Coprocessor

- Operates in conjunction with and under the control of another processor

- Usually

- Special-purpose processor

- Performs a single task

- Operates at high speed

- Example: floating point accelerator

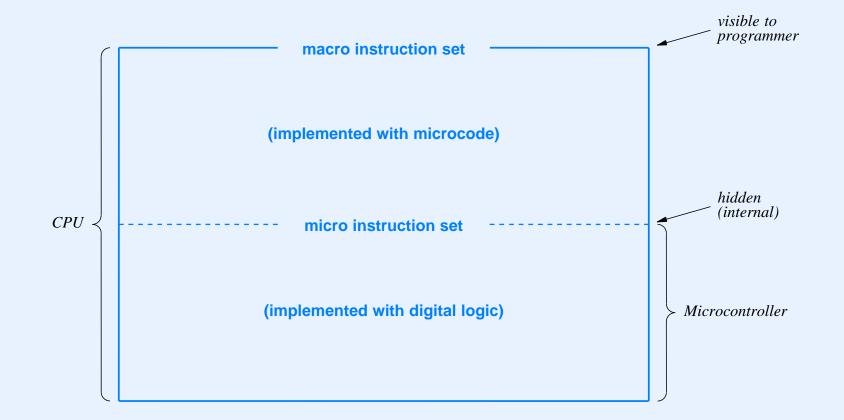

## Microcontroller

- Programmable device

- Dedicated to control of a physical system

- Example: control an automobile engine or grocery store door

- Negative: extremely limited (slow processor and tiny memory)

- Positive: very low power consumption

#### Example Steps A Microcontroller Performs (Automatic Door)

do forever {

wait for the sensor to be tripped;

turn on power to the door motor;

wait for a signal that indicates the

door is open;

wait for the sensor to reset;

delay ten seconds;

turn off power to the door motor;

## **Embedded System Processor**

- Runs sophisticated electronic device

- May be more powerful than microcontroller

- Generally low power consumption

- Example: control DVD player, including commands received from a remote control as well as from the front panel

#### **General-Purpose Processor**

- Most powerful type of processor

- Completely programmable

- Full functionality

- Power consumption is secondary consideration

- Example: CPU in a personal computer

#### **Processor Implementation**

- Originally: discrete logic

- Later: single circuit board

- Even later: single chip

- Now: usually part of a single chip

# **Definition Of Programmable Device**

- To a software engineer programming means

- Writing, compiling, and loading code into memory

- Executing the resulting memory image

- To a hardware engineer a *programmable* device

- Has a processor separate from the program it runs

- May have the program burned onto a chip

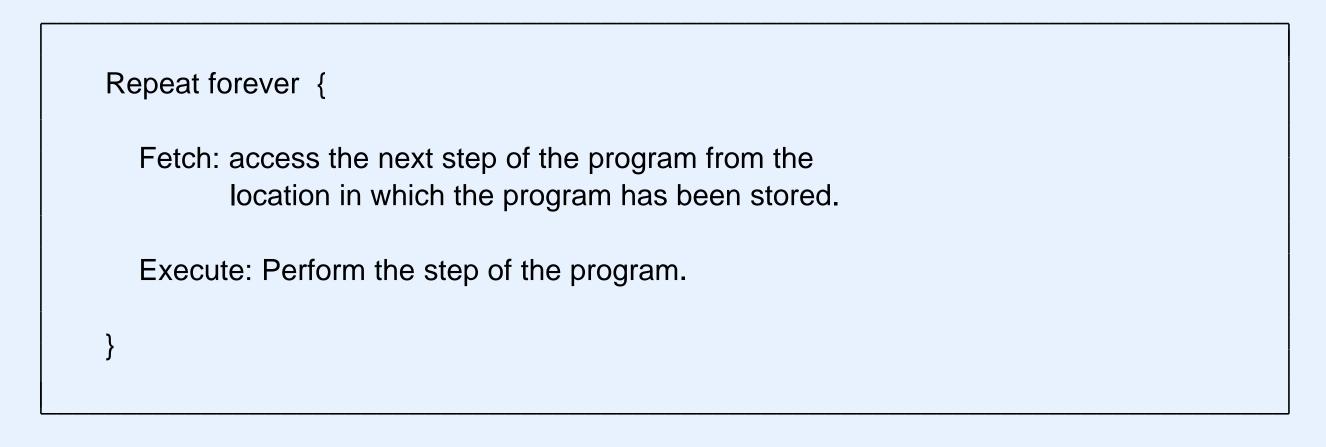

# **Fetch-Execute Cycle**

- Basis for programmable processors

- Allows processor to move through program steps automatically

- Implemented by processor hardware

- At some level, every programmable processor implements a fetch-execute cycle

#### **Fetch-Execute Algorithm**

• Note: we will discuss in more detail later

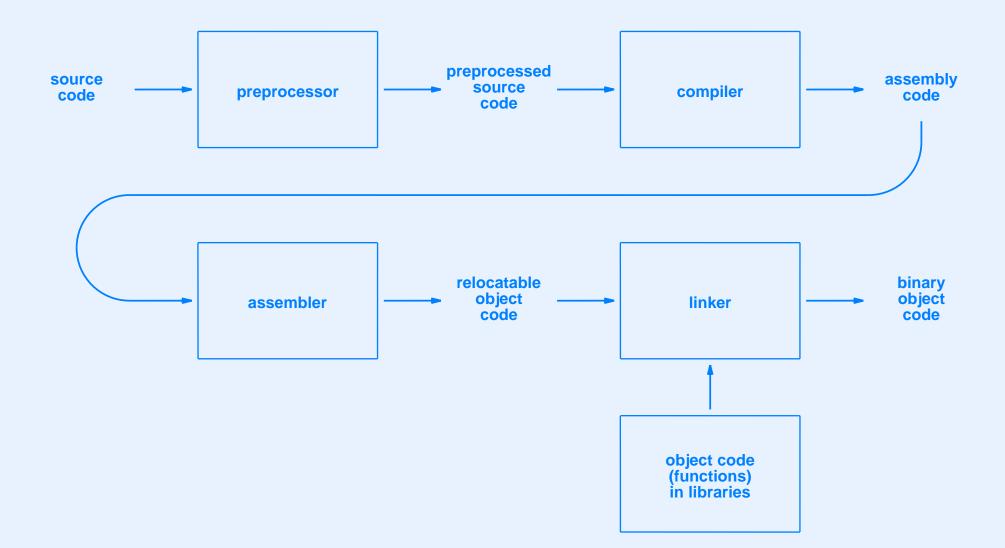

#### **Program Translation**

- Processors require a program to be

- In memory

- Represented in binary

- Programmers prefer a program to be

- Readable by humans

- In a *High Level Language*

- Solution: allow programmers to write code in a readable high-level language and translate to binary

- Use computer software to perform the translation

#### **Illustration Of Program Translation**

# **Clock Rate And Instruction Rate**

- Clock rate

- Rate at which gates are clocked

- Provides a measure of the underlying hardware speed

- Instruction rate

- Measures the number of instructions a processor can *execute* per unit time

- On some processors, a given instruction may take more clock cycles than other instructions

- Example: multiplication may take longer than addition

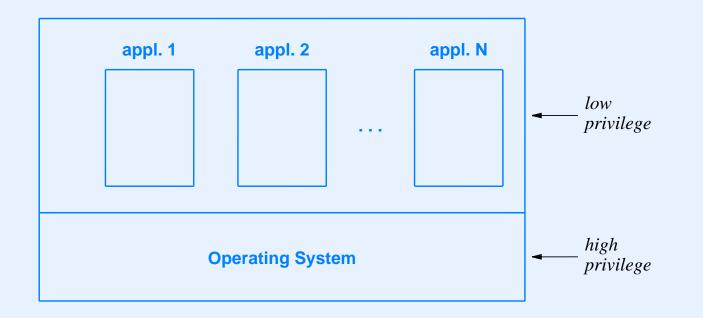

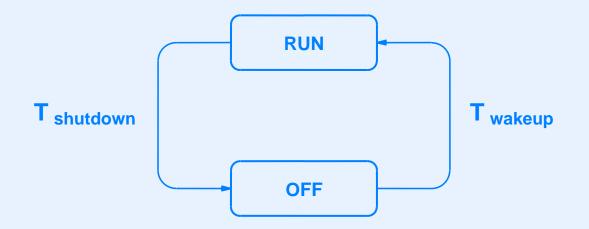

# **Stopping A Processor**

- Processor runs fetch-execute indefinitely

- Software must plan next step

- Two possibilities when last step of computation finishes

- Smallest embedded systems: code enters a loop testing for a change in input

- Larger systems: operating system runs and executes an infinite loop

- Note: to reduce power consumption, hardware may provide a way to put processor to sleep until I/O activity occurs (covered later in the course)

# **Starting A Processor**

- Processor hardware includes a *reset* line that stops the fetch-execute cycle

- For power-down: reset line is asserted

- During power-up, logic holds the reset until the processor and memory are initialized

- Power-up steps known as *bootstrap*

#### **Summary**

- Processor performs a computation involving multiple steps

- Many types of processors

- Coprocessor

- Microcontroller

- Embedded system processor

- General-purpose processor

- Arithmetic Logic Unit (ALU) performs basic arithmetic and Boolean operations

# Summary (continued)

- Hardware in programmable processor runs fetch-execute cycle

- Until a processor is powered down, fetch-execute must continue

# **Questions?**

#### Module V

Processor Types And Instruction Sets

• Minimum set is sufficient, but inconvenient

- Minimum set is sufficient, but inconvenient

- Extremely large set is convenient, but inefficient

- Minimum set is sufficient, but inconvenient

- Extremely large set is convenient, but inefficient

- Architect must consider additional factors

- Physical size of processor chip

- Expected use

- Power consumption

- Minimum set is sufficient, but inconvenient

- Extremely large set is convenient, but inefficient

- Architect must consider additional factors

- Physical size of processor chip

- Expected use

- Power consumption

- Minimum set is sufficient, but inconvenient

- Extremely large set is convenient, but inefficient

- Architect must consider additional factors

- Physical size of processor chip

- Expected use

- Power consumption

- Tradeoffs mean a variety of designs exist

## **Instruction Set Architecture**

- Idea pioneered by IBM

- Allows multiple, compatible models

- Define

- Set of instructions

- Operands and meaning

- Do not define

- Implementation details

- Processor speed

# **A Few Choices**

- Functionality: what the instructions provide

- Arithmetic (integer or floating point)

- Logic (bit manipulation and testing)

- Control (branching, function call)

- Other (graphics, data conversion)

- Format: representation for each instruction

- Semantics: effect when instruction is executed

- An *Instruction Set Architecture* includes all of the above

### **Parts Of An Instruction**

- *Opcode* specifies operation to be performed

- *Operands* specify data values on which to operate

- *Result location* specifies where result is to be placed

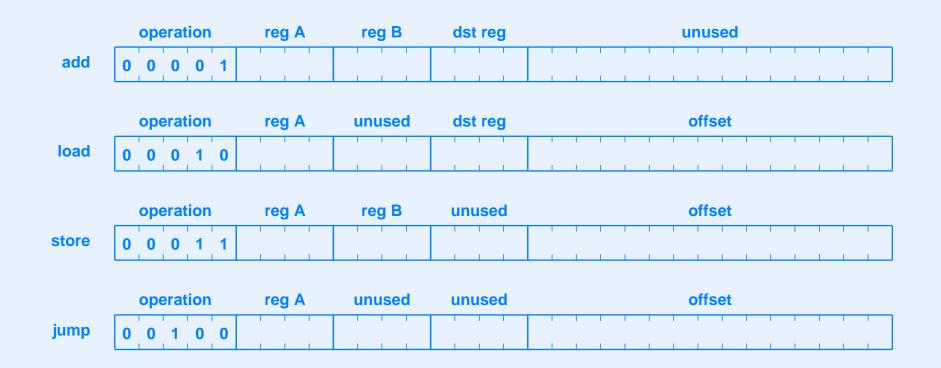

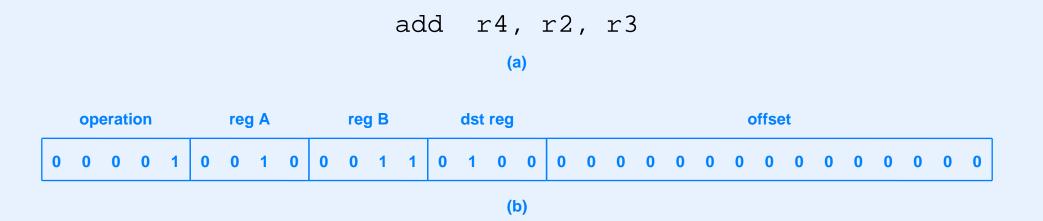

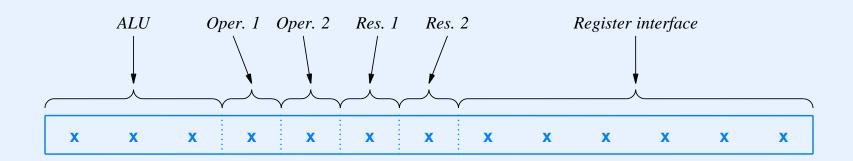

#### **Instruction Format**

- Instruction represented as sequence of bits in memory (usually multiples of bytes)

- Typically

- Opcode at beginning of instruction

- Operands follow opcode

| opcode | operand 1 | operand 2 |  |

|--------|-----------|-----------|--|

|--------|-----------|-----------|--|

# **Instruction Length**

- Fixed-length

- Every instruction is same size

- Hardware is less complex

- Hardware can run faster

- Wasted space: some instructions do not use all the bits

- Variable-length

- Some instructions shorter than others

- Allows instructions with no operands, a few operands, or many operands

- Efficient use of memory (no wasted space)

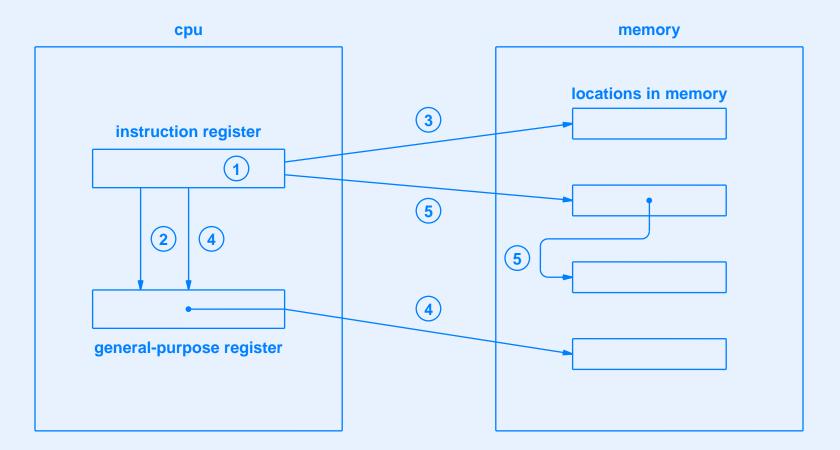

### **General-Purpose Registers**

- High-speed storage mechanism

- Part of the processor (on chip)

- Each register holds an integer or a pointer

- Numbered from 0 through N-1

- Basic uses

- Temporary storage during computation

- Operand for arithmetic operation

- Note: some processors require all operands for an arithmetic operation to come from general-purpose registers

# **Floating Point Registers**

- Usually separate from general-purpose registers

- Each holds one floating-point value

- Floating point registers are operands for floating point arithmetic

### **Example Of Programming With Registers**

- Task

- Start with variables X and Y in memory

- Add X and Y and place the result in variable Z (also in memory)

### **Example Of Programming With Registers**

- Task

- Start with variables X and Y in memory

- Add X and Y and place the result in variable Z (also in memory)

- Example steps

- Load a copy of X into register 1

- Load a copy of Y into register 2

- Add the value in register 1 to the value in register 2, and put the result in register 3

- Store a copy of the value in register 3 in Z

- Note: the above assumes registers 1, 2, and 3 are available

# Terminology

- Register spilling

- Occurs when a register is needed for a computation and all registers contain values

- General idea

- \* Save current contents of register(s) in memory

- \* Reload registers(s) from memory when values are needed

- Register allocation

- Refers to choosing which values to keep in registers at a given time

- Performed by programmer or compiler

#### **Double Precision**

- Refers to value that is twice as large as a standard integer

- Most processors do not have dedicated registers for double precision computation

- Approach taken: programmer must use a contiguous pair of registers to hold a double precision value

- Example: multiplication of two 32-bit integers

- Result can require 64 bits

- Programmer specifies that result goes into a pair of registers (e.g., 4 and 5)

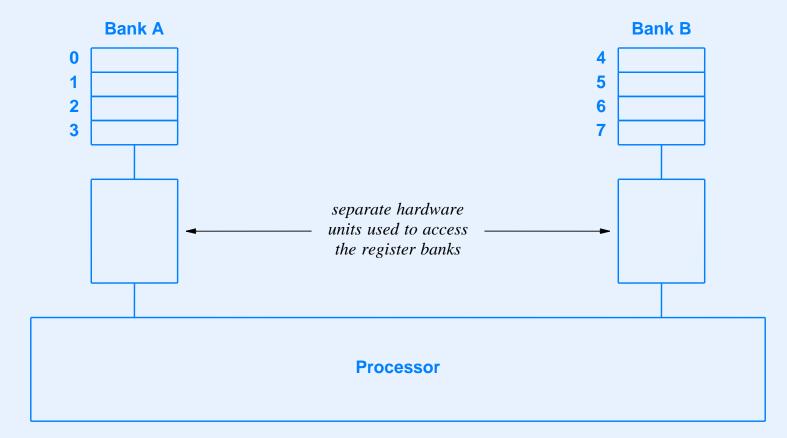

# **Register Banks**

- Registers partitioned into disjoint sets called *banks*

- Additional hardware detail

- Optimizes performance

- Complicates programming

# **Register Banks**

- Registers partitioned into disjoint sets called *banks*

- Additional hardware detail

- Optimizes performance

- Complicates programming

# **Typical Register Bank Scheme**

- Registers divided into two banks

- ALU instruction that takes two operands must have one operand from each bank

- Programmer must ensure operands are in separate banks

- Note: having two operands from the same bank will cause a run-time error

#### Why Register Banks Are Used

• Parallel hardware facilities allow simultaneous access of both banks

• Access takes half as long as using a single bank

#### **Consequence For Programmers**

- Even trivial programs cause problems

- Example

$R \leftarrow X + Y$  $S \leftarrow Z - X$  $T \leftarrow Y + Z$

- Operands must be assigned to banks

- No feasible choice for the above

### **Register Conflicts**

- Occur when operands specify same register bank

- May be reported by compiler / assembler

- Programmer must rewrite code or insert extra instruction to copy an operand value to the opposite register bank

- In the previous example

- Start with Y and Z in the same bank

- Before adding Y and Z, copy one to another bank

## **Two Types Of Instruction Sets**

- CISC: Complex Instruction Set Computer

- RISC: Reduced Instruction Set Computer

### **CISC Instruction Set**

- Many instructions (often hundreds)

- Given instruction can require arbitrary time to compute

- Example: Intel/AMD (x86/x64) or IBM instruction set

- Typical complex instructions

- Move graphical item on bitmapped display

- Copy or clear a region of memory

- Perform a floating point computation

#### **RISC Instruction Set**

- Few instructions (typically 32 or 64)

- Each instruction executes in one clock cycle

- Example: MIPS or ARM instruction set

- Omits complex instructions

- No floating-point instructions

- No graphics instructions

- Sequence of instructions needed to perform complex action

# **Instruction Pipeline**

- A major idea in processor design

- Also called *execution pipeline*

- Optimizes performance

- Permits processor to complete more instructions per unit time

- Typically used with RISC instruction set

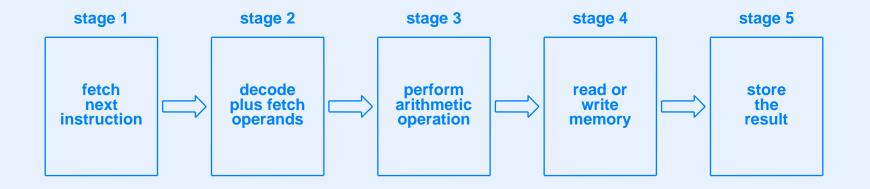

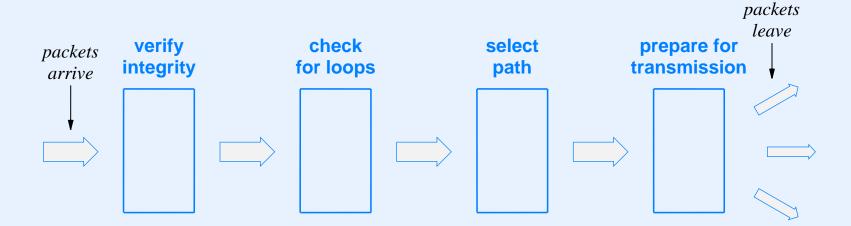

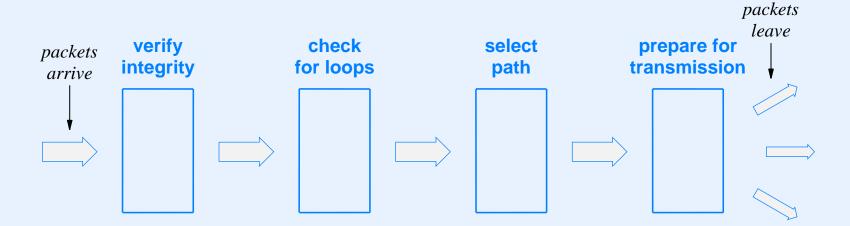

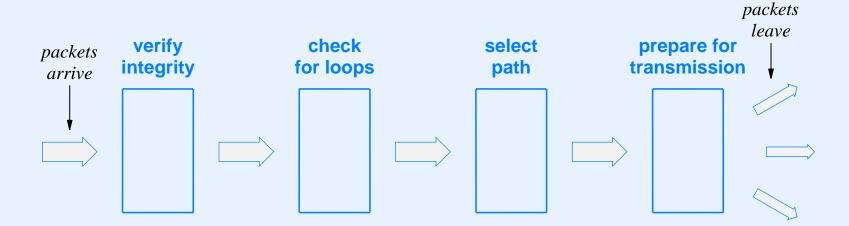

# **Basic Steps In A Fetch-Execute Cycle**

- Fetch the next instruction

- Decode the instruction and fetch operands from registers

- Perform the arithmetic operation specified by the opcode

- Perform memory read or write, if needed

- Store result back to the registers

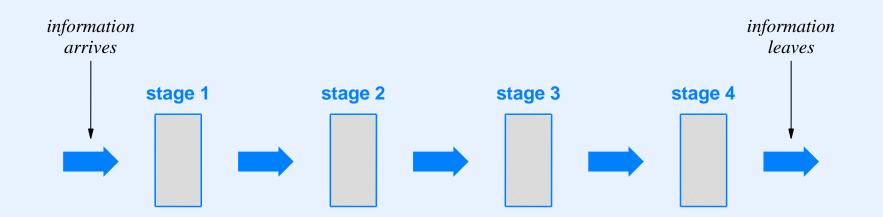

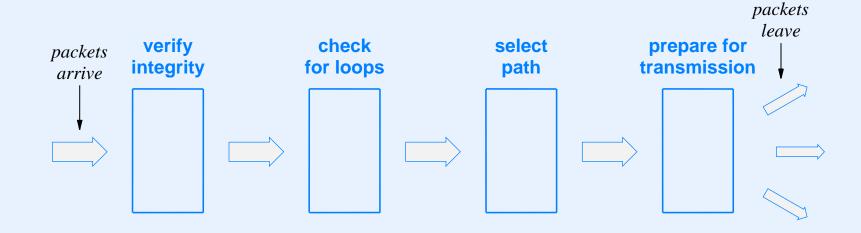

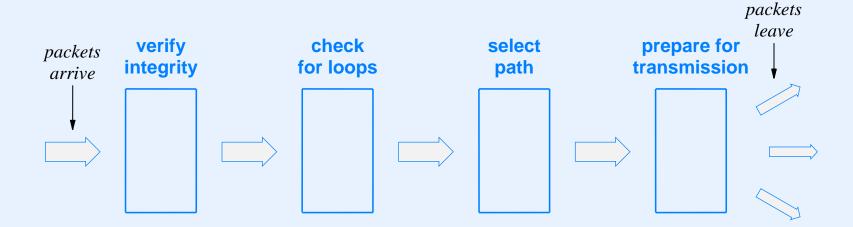

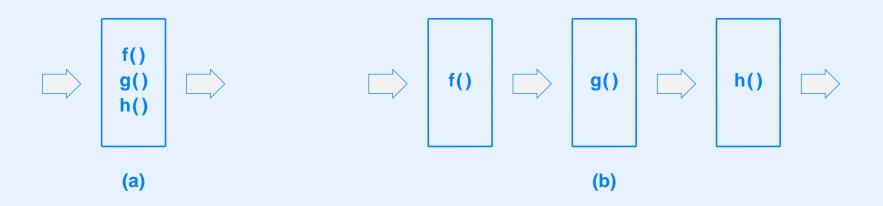

### **Instruction Pipeline Approach**

- Build separate hardware block for each step of the fetch-execute cycle

- Arrange hardware to pass an instruction through the sequence of hardware blocks

- Allows step K of one instruction to execute while step K-1 of next instruction executes

- Result is an *execution pipeline*

#### **Illustration Of An Execution Pipeline**

- Example pipeline has five *stages*

- All stages operate at the same time

- Instruction passes through like a factory assembly line

### **Illustration Of Instructions In A Pipeline**

| _    | clock | stage 1 | stage 2 | stage 3 | stage 4 | stage 5 |

|------|-------|---------|---------|---------|---------|---------|

| Time | 1     | inst. 1 |         |         |         | -       |

|      | 2     | inst. 2 | inst. 1 | -       |         | -       |

|      | 3     | inst. 3 | inst. 2 | inst. 1 |         | -       |

|      | 4     | inst. 4 | inst. 3 | inst. 2 | inst. 1 | -       |

|      | 5     | inst. 5 | inst. 4 | inst. 3 | inst. 2 | inst. 1 |

|      | 6     | inst. 6 | inst. 5 | inst. 4 | inst. 3 | inst. 2 |

| . ↓  | 7     | inst. 7 | inst. 6 | inst. 5 | inst. 4 | inst. 3 |

|      | 8     | inst. 8 | inst. 7 | inst. 6 | inst. 5 | inst. 4 |

# **Pipeline Speed**

- All stages operate in parallel

- Given stage can start to process a new instruction as soon as current instruction finishes

- Effect: N-stage pipeline can operate on N instructions simultaneously, producing speedup

- Result

- One instruction completes every time pipeline moves

- For RISC processor, one instruction completes on every clock cycle

- Comparison: without a pipeline, each instruction would take five clock cycles

# **Significance Of A Pipeline To A Programmer**

- Pipeline is *transparent* to programmers (i.e., is automatic)

- Execution speed

- Is never worse than a processor without a pipeline

- May be K times faster than processor without a pipeline

- Pipeline *stalls* (i.e., pauses) if item is not available when a stage needs the item

- Programmer who does not understand pipeline can produce code that stalls frequently

#### **Example Of Instructions That Cause A Stall**

- Consider code that

- Performs addition and subtraction operations

- Uses registers A through E for operands and results

- Example instruction sequence

Instruction K:  $C \leftarrow add \land B$ Instruction K+1:  $D \leftarrow subtract \mathrel{E} C$

- Instruction K+1 must wait for operand C to be computed

- Result is a *stall*

### **Effect Of Stall On Pipeline**

|      | clock | stage 1<br>fetch<br>instruction | stage 2<br>fetch<br>operands | stage 3<br>ALU<br>operation | stage 4<br>access<br>memory | stage 5<br>write<br>results |

|------|-------|---------------------------------|------------------------------|-----------------------------|-----------------------------|-----------------------------|

|      | 1     | inst. K                         | inst. K-1                    | inst. K-2                   | inst. K-3                   | inst. K-4                   |

| Time | 2     | inst. K+1                       | inst. K                      | inst. K-1                   | inst. K-2                   | inst. K-3                   |

|      | 3     | inst. K+2                       | (inst. K+1)                  | inst. K                     | inst. K-1                   | inst. K-2                   |

|      | 4     | (inst. K+2)                     | (inst. K+1)                  | -                           | inst. K                     | inst. K-1                   |

|      | 5     | (inst. K+2)                     | (inst. K+1)                  | -                           | -                           | inst. K                     |

|      | 6     | (inst. K+2)                     | inst. K+1                    | -                           | -                           | -                           |

|      | 7     | inst. K+3                       | inst. K+2                    | inst. K+1                   | -                           | -                           |

|      | 8     | inst. K+4                       | inst. K+3                    | inst. K+2                   | inst. K+1                   | -                           |

|      | 9     | inst. K+5                       | inst. K+4                    | inst. K+3                   | inst. K+2                   | inst. K+1                   |

|      | 10    | inst. K+6                       | inst. K+5                    | inst. K+4                   | inst. K+1                   | inst. K+2                   |

• We say a *bubble* passes through pipeline

## **Actions That Cause A Pipeline Stall**

- Access external storage (i.e., memory reference)

- Invoke a coprocessor (i.e., I/O)

- Branch to a new location

- Call a subroutine

# **Achieving Maximum Speed**

- Program must be written to accommodate instruction pipeline

- To minimize stalls

- Avoid introducing unnecessary branches

- Delay references to result register(s)

- A contradiction

- Good software engineering practice divides a large program into smaller functions

- A function call stalls the pipelining

#### **Example Of Avoiding Stalls**

$$C \leftarrow add A B$$

$$D \leftarrow subtract E C$$

$$F \leftarrow add G H$$

$$J \leftarrow subtract I F$$

$$M \leftarrow add K L$$

$$P \leftarrow subtract M N$$

$$(a)$$

- $C \leftarrow add A B$

- $F \leftarrow add G H$

- $M \leftarrow add K L$

- $D \leftarrow subtract E C$

- $J \leftarrow subtract I F$

- $P \leftarrow subtract M N$ (b)

- Stalls eliminated by rearranging (a) to (b)

- Compilers for RISC processors usually optimize code to avoid stalls

# **A Note About Pipelines**

- We can think of pipelining as an automatic optimization

- Hardware speeds up processing if possible

- If speedup is not possible, hardware is still correct

- Consequence: code that is not optimized will work correctly, but may run slower than necessary

# Forwarding

- Hardware optimization to avoid a stall

- Allows ALU to reference result in next instruction

- Example

Instruction K:  $C \leftarrow add \land B$ Instruction K+1:  $D \leftarrow subtract \mathrel{E} C$

- Forwarding hardware

- Passes result of *add* operation directly to ALU without waiting to store it in a register

- Ensures the value arrives by the time subtract instruction reaches the pipeline stage for execution

# **No-Op Instruction**

- Often included in RISC instruction sets

- May seem unnecessary

- Has no effect on

- Registers

- Memory

- Program counter

- Computation

- Purpose: can be inserted to avoid instruction stalls

# Use Of No-Op

• Example

Instruction K: $C \leftarrow add \land B$ Instruction K+1:no-opInstruction K+2: $D \leftarrow subtract \mathrel E \mathrel C$

- If forwarding is available, no-op allows time for result from register *C* to be fetched for *subtract* operation

- Compilers insert no-op instructions to optimize performance

# **Types Of Opcodes**

- Operations usually classified into groups

- An example categorization

- Arithmetic instructions (integer arithmetic)

- Logical instructions (also called Boolean)

- Data access and transfer instructions

- Conditional and unconditional branch instructions

- Floating point instructions

- Processor control instructions

- Graphics instructions

#### **Program Counter**

- Hardware register

- Used during fetch-execute cycle

- Gives address of next instruction to execute

- Also known as *instruction pointer* or *instruction counter*

# **Fetch-Execute Algorithm Details**

Assign the program counter an initial program address.

Repeat forever {

Fetch: access the next step of the program from the location given by the program counter.

Set an internal address register, A, to the address beyond the instruction that was just fetched.

Execute: Perform the step of the program.

Copy the contents of address register A to the program counter.

# **Branches And Fetch Execute**

- Absolute branch

- Typically named *jump*

- Operand is an address

- Assigns operand value to internal register A

- Relative branch

- Typically named br

- Operand is a signed value

- Adds operand to internal register A

# **Subroutine Call**

- Jump to subroutine (*jsr* instruction)

- Similar to a *jump*

- Saves value of internal register A

- Replaces *A* with operand address

- Return from subroutine (*ret* instruction)

- Retrieves value saved during jsr

- Replaces *A* with saved value

## **Passing Arguments**

- Multiple methods are used

- Choice depends on language/compiler as well as hardware

- Examples

- Store arguments in memory

- Store arguments in special-purpose hardware registers

- Store arguments in general-purpose registers

- Many techniques also used to return result from *function*

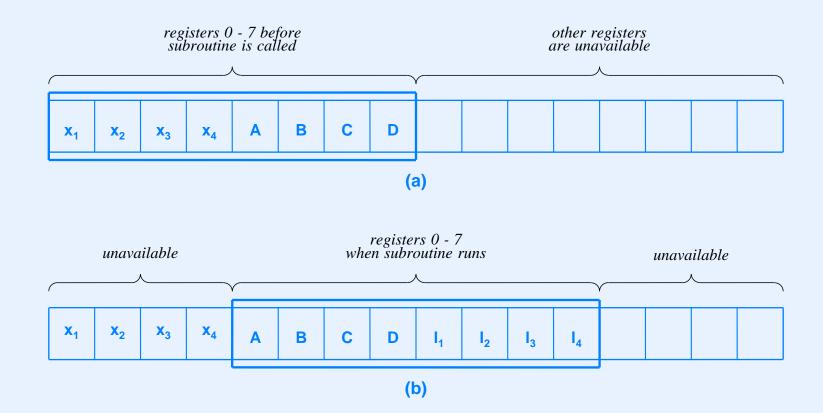

## **Register Window**

- Hardware optimization for argument passing

- Processor contains many general-purpose registers

- Only a small subset of registers visible at any time

- Caller places arguments in reserved registers

- During procedure call, register window moves to hide old registers and expose new registers

# **Illustration Of Register Window**

- (a) registers before calling a subroutine

- (b) registers when the subroutine runs

# **An Example Instruction Set**

- Known as *MIPS* instruction set

- Early RISC design

- Minimalistic

- Only 32 instructions

#### **MIPS Instruction Set (Part 1)**

| Instruction            | Meaning                                |  |

|------------------------|----------------------------------------|--|

| Arithmetic             |                                        |  |

| add                    | integer addition                       |  |

| subtract               | integer subtraction                    |  |

| add immediate          | integer addition (register + constant) |  |

| add unsigned           | unsigned integer addition              |  |

| subtract unsigned      | unsigned integer subtraction           |  |

| add immediate unsigned | unsigned addition with a constant      |  |

| move from coprocessor  | access coprocessor register            |  |

| multiply               | integer multiplication                 |  |

| multiply unsigned      | unsigned integer multiplication        |  |

| divide                 | integer division                       |  |

| divide unsigned        | unsigned integer division              |  |

| move from Hi           | access high-order register             |  |

| move from Lo           | access low-order register              |  |

| Logical (Boolean)      |                                        |  |

| and                    | logical and (two registers)            |  |

| or                     | logical or (two registers)             |  |

| and immediate          | and of register and constant           |  |

or of register and constant

Shift register left N bits

Shift register right N bits

or immediate

shift left logical

shift right logical

#### **MIPS Instruction Set (Part 2)**

| Instruction                                                                                                                          | Meaning                                                                                                                                                                                            |  |

|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Data Transfer                                                                                                                        |                                                                                                                                                                                                    |  |

| load word<br>store word<br>load upper immediate<br>move from coproc. register                                                        | load register from memory<br>store register into memory<br>place constant in upper sixteen<br>bits of register<br>obtain a value from a coprocessor                                                |  |

| Conditional Branch                                                                                                                   |                                                                                                                                                                                                    |  |

| branch equal<br>branch not equal<br>set on less than<br>set less than immediate<br>set less than unsigned<br>set less than immediate | branch if two registers equal<br>branch if two registers unequal<br>compare two registers<br>compare register and constant<br>compare unsigned registers<br>compare unsigned register and constant |  |

| Unconditional Branch<br>jump<br>jump register<br>jump and link                                                                       | go to target address<br>go to address in register<br>procedure call                                                                                                                                |  |

## **MIPS Floating Point Instructions**

| Instruction                    | Meaning                             |  |

|--------------------------------|-------------------------------------|--|

| Arithmetic                     |                                     |  |

| FP add                         | floating point addition             |  |

| FP subtract                    | floating point subtraction          |  |

| FP multiply                    | floating point multiplication       |  |

| FP divide                      | floating point division             |  |

| FP add double                  | double-precision addition           |  |

| FP subtract double             | double-precision subtraction        |  |

| FP multiply double             | double-precision multiplication     |  |

| FP divide double Data Transfer | double-precision division           |  |

| load word coprocessor          | load value into FP register         |  |

| store word coprocessor         | store FP register to memory         |  |

| Conditional Branch             |                                     |  |

| branch FP true                 | branch if FP condition is true      |  |

| branch FP false                | branch if FP condition is false     |  |

| FP compare single              | compare two FP registers            |  |

| FP compare double              | compare two double precision values |  |

# **Aesthetic Aspects Of Instruction Sets**

- Elegance

- Balanced

- No frivolous or useless instructions

- Orthogonality

- No unnecessary duplication

- No overlap among instructions

- Ease of programming

- Instructions match programmer's intuition

- Instructions are free from arbitrary restrictions

# **Principle Of Orthogonality**

- Specifies that each instruction should perform a unique task

- No instruction duplicates or overlaps another

# **Condition Codes**

- Extra hardware bits (not part of general-purpose registers)

- Set by ALU each time an instruction produces a result

- Used to indicate

- Overflow

- Underflow

- Whether result is positive, negative, or zero

- Other exceptions

- Tested in *conditional branch* instruction

#### **Example Of Condition Code**

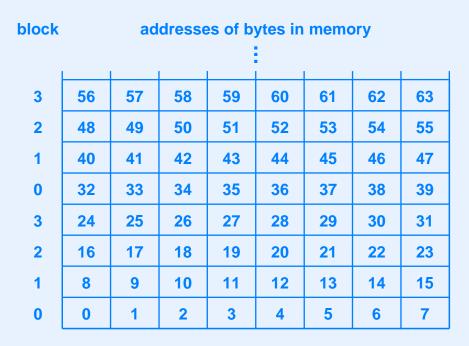

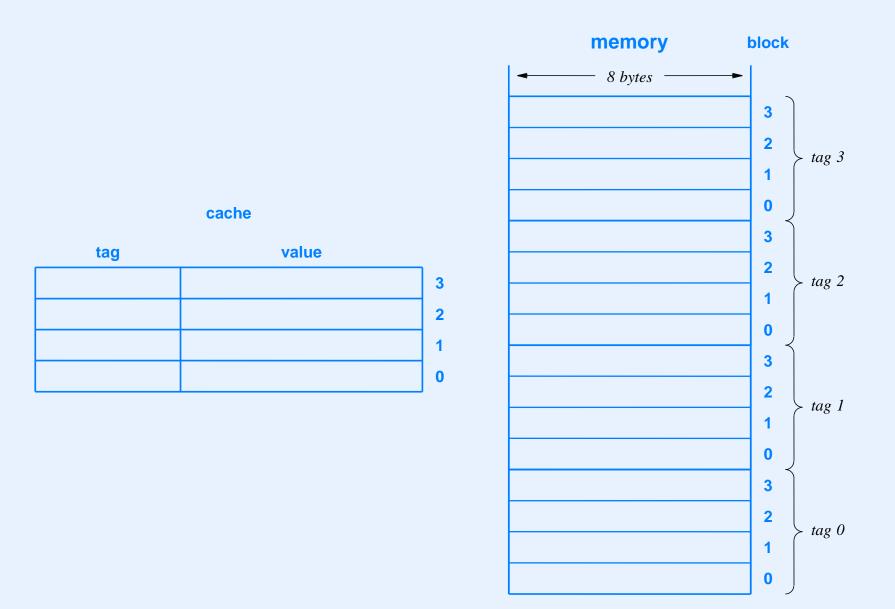

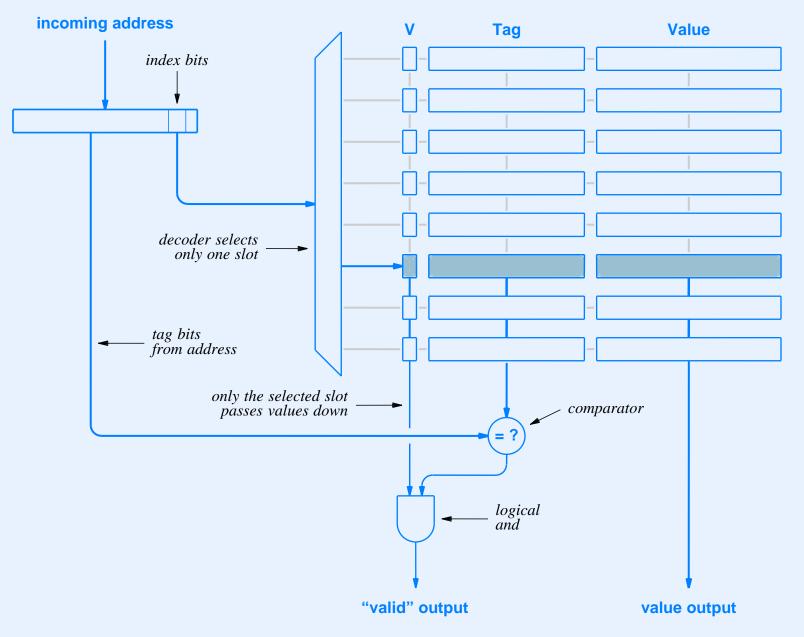

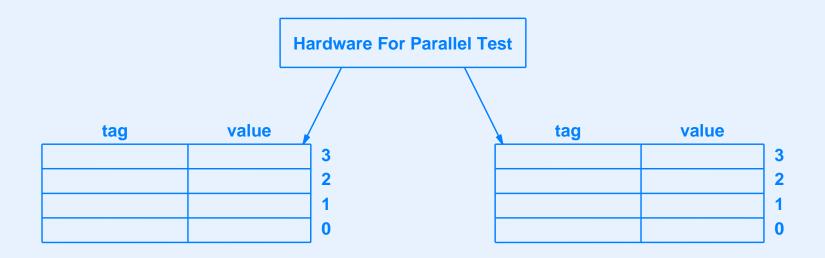

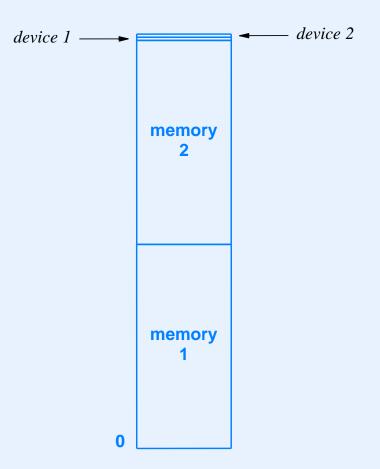

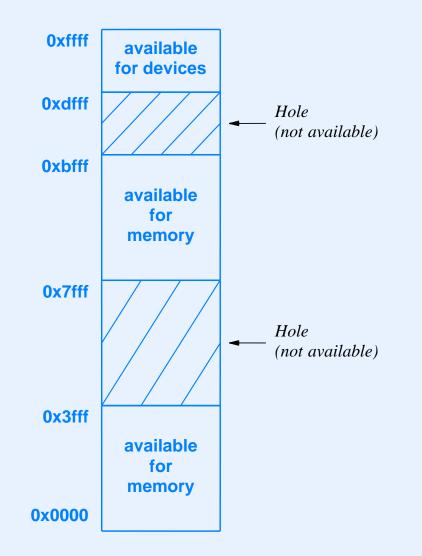

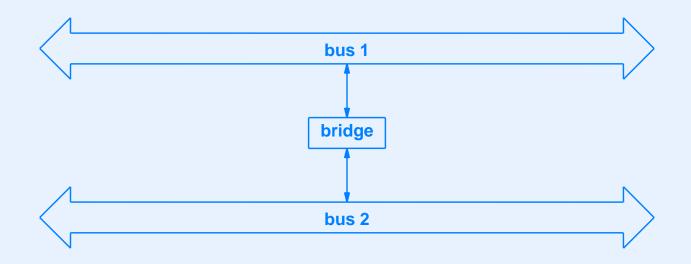

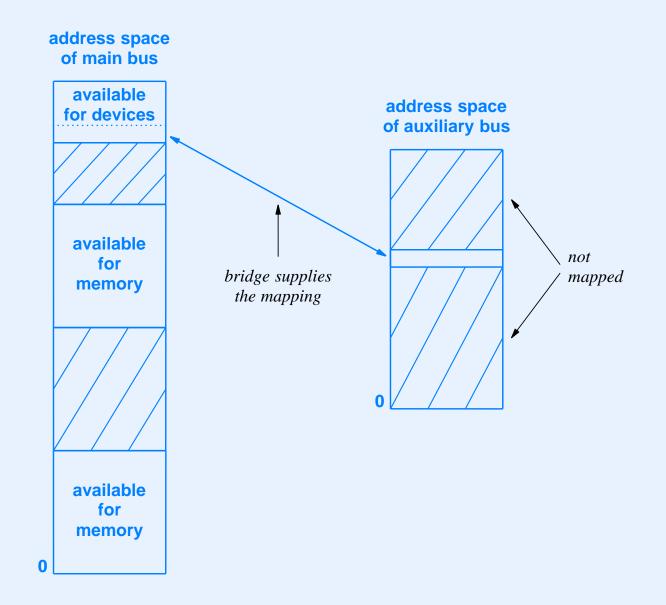

| cmp | r4, r5 | # compare regs. 4 & 5, and set condition code  |