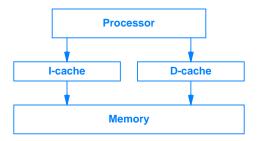

**Figure 12.6** A Modified Harvard Architecture with separate instruction and data caches leading to the same underlying memory.